Hi Guys

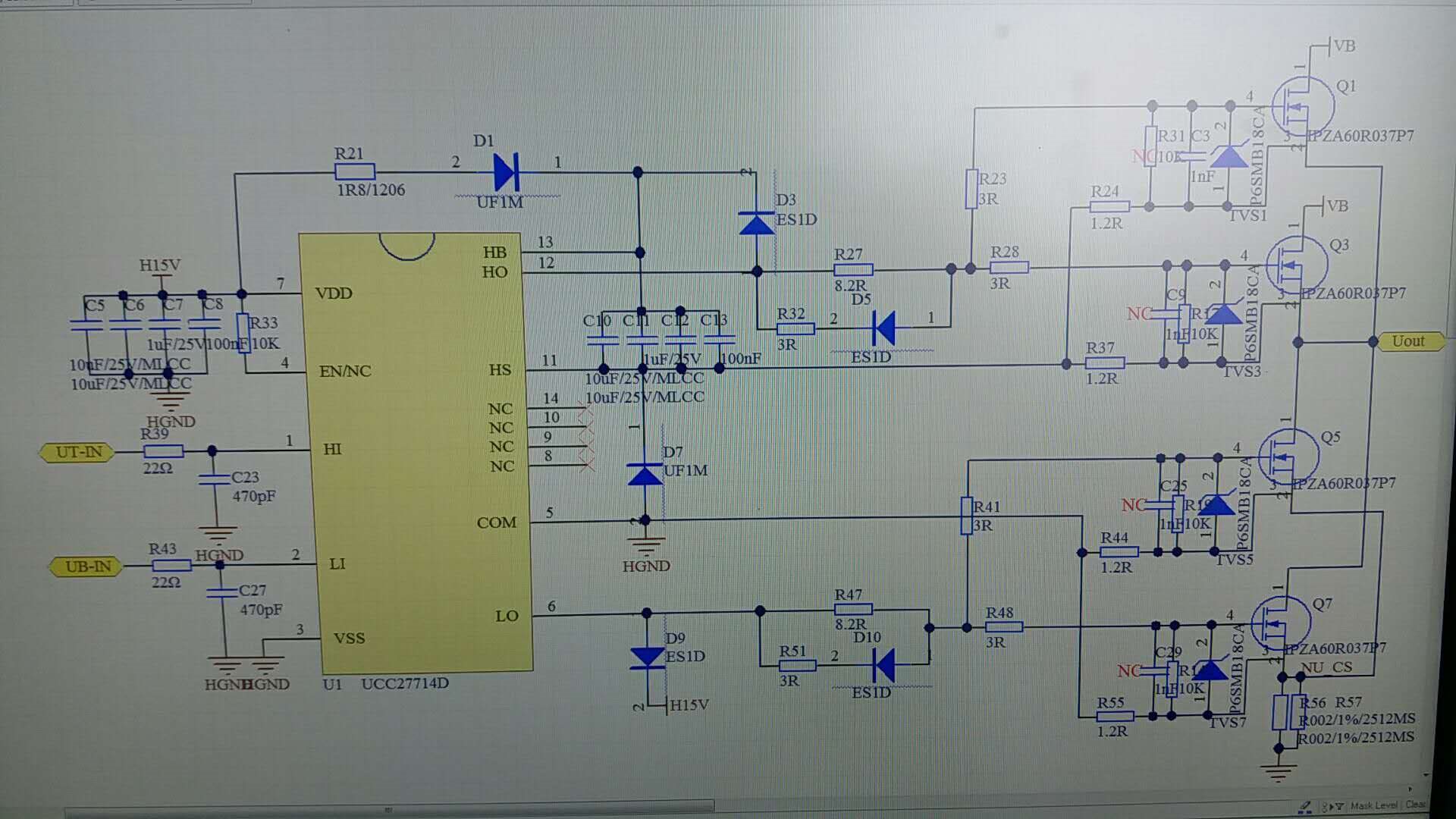

Our customer are using our UCC27714 to drive a half bridge mosfet in three-phase inverter application. high side and low side mosfet contain two mosfets in parallel. you can see the Schematic in which I just show U phase. there are V phase and W phase that are the same as U phase.

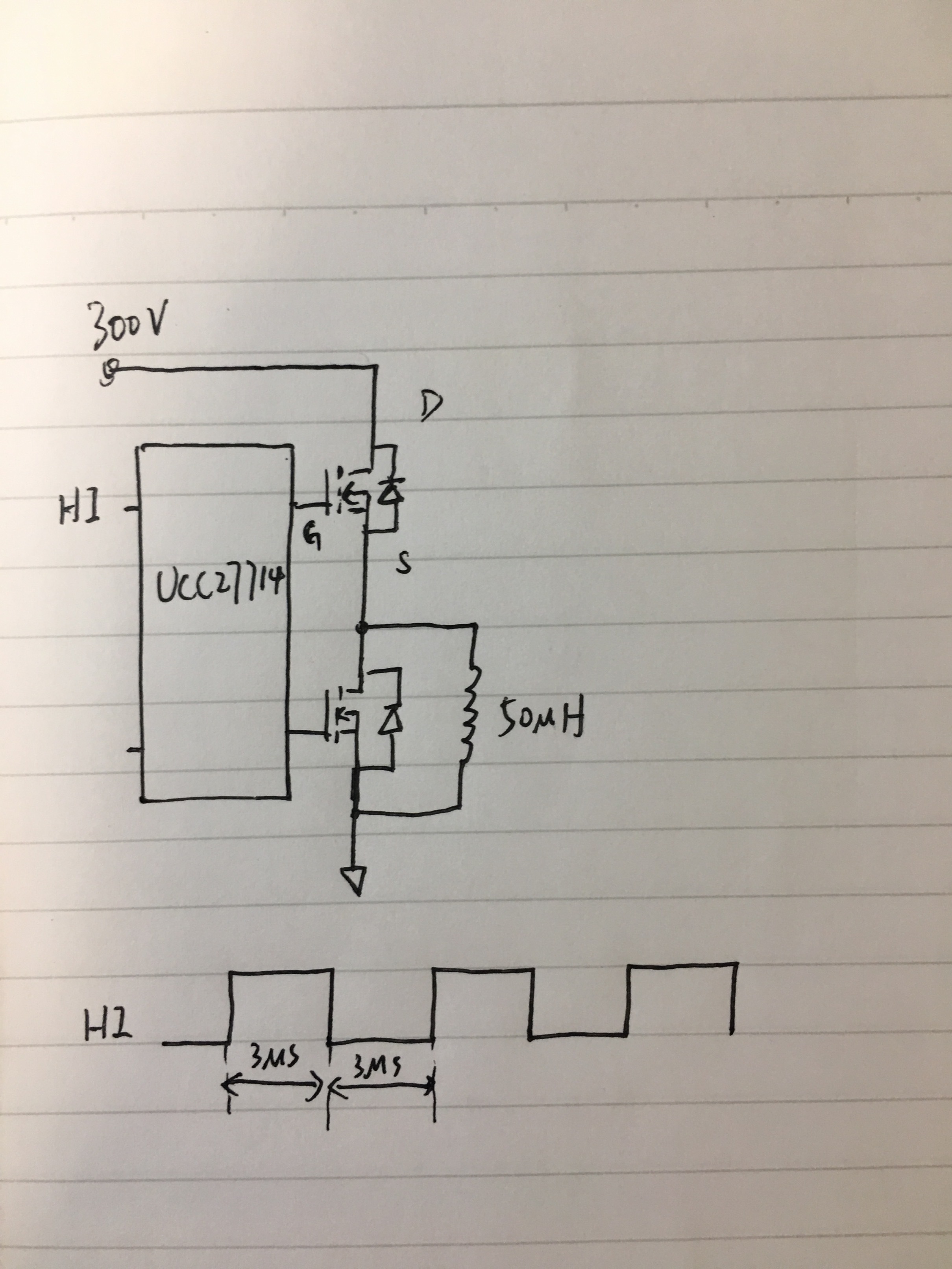

When customer do the double pulse test. Test circuit is below: which we call it high side mos test.

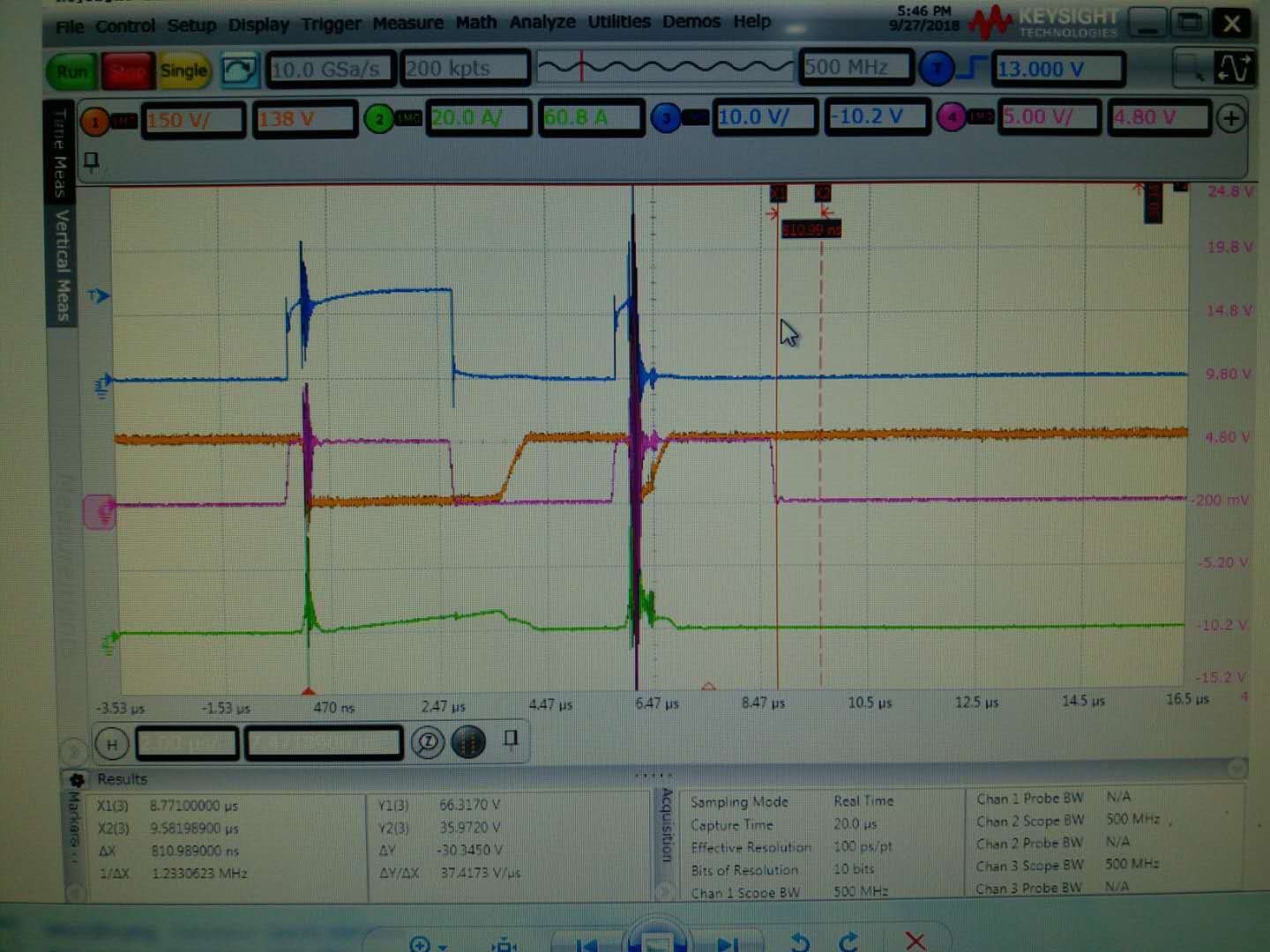

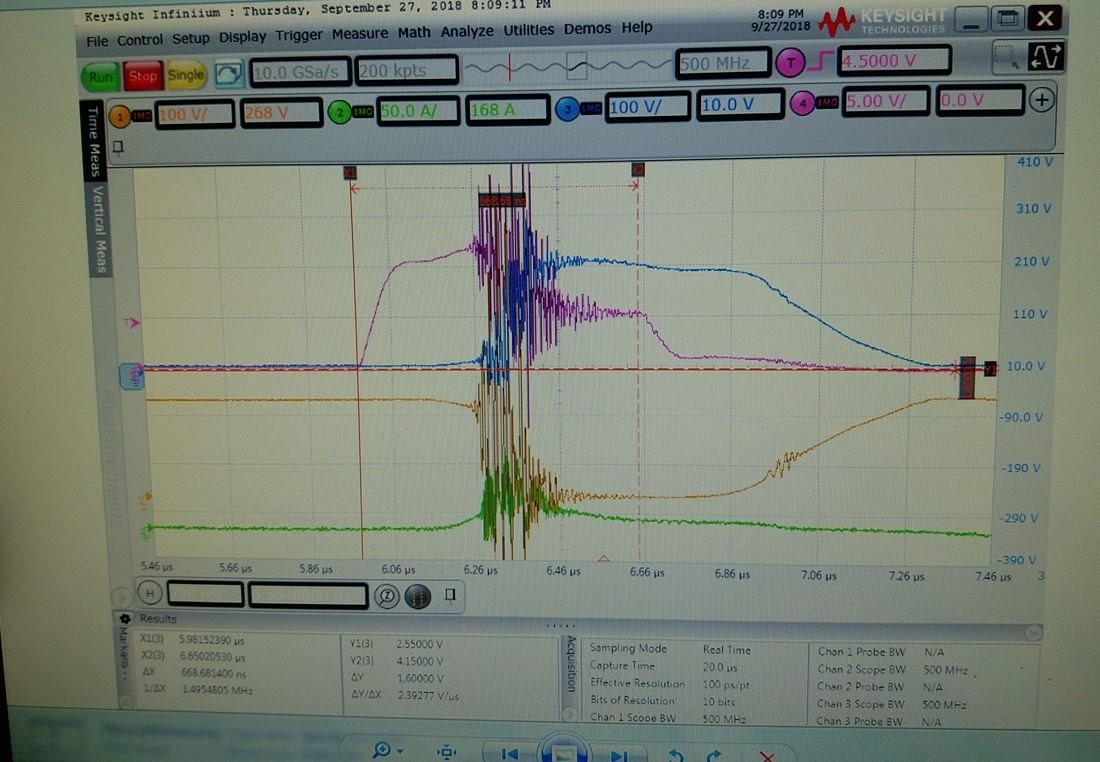

At this test, we found an issue: Sometimes, the first pulse is OK, but at the second pulse ON, the high side driver will turn off abnormally. you can see below:

CH1:Vds; CH2: Ids; CH3: HO Pin; CH4: HI Pin;

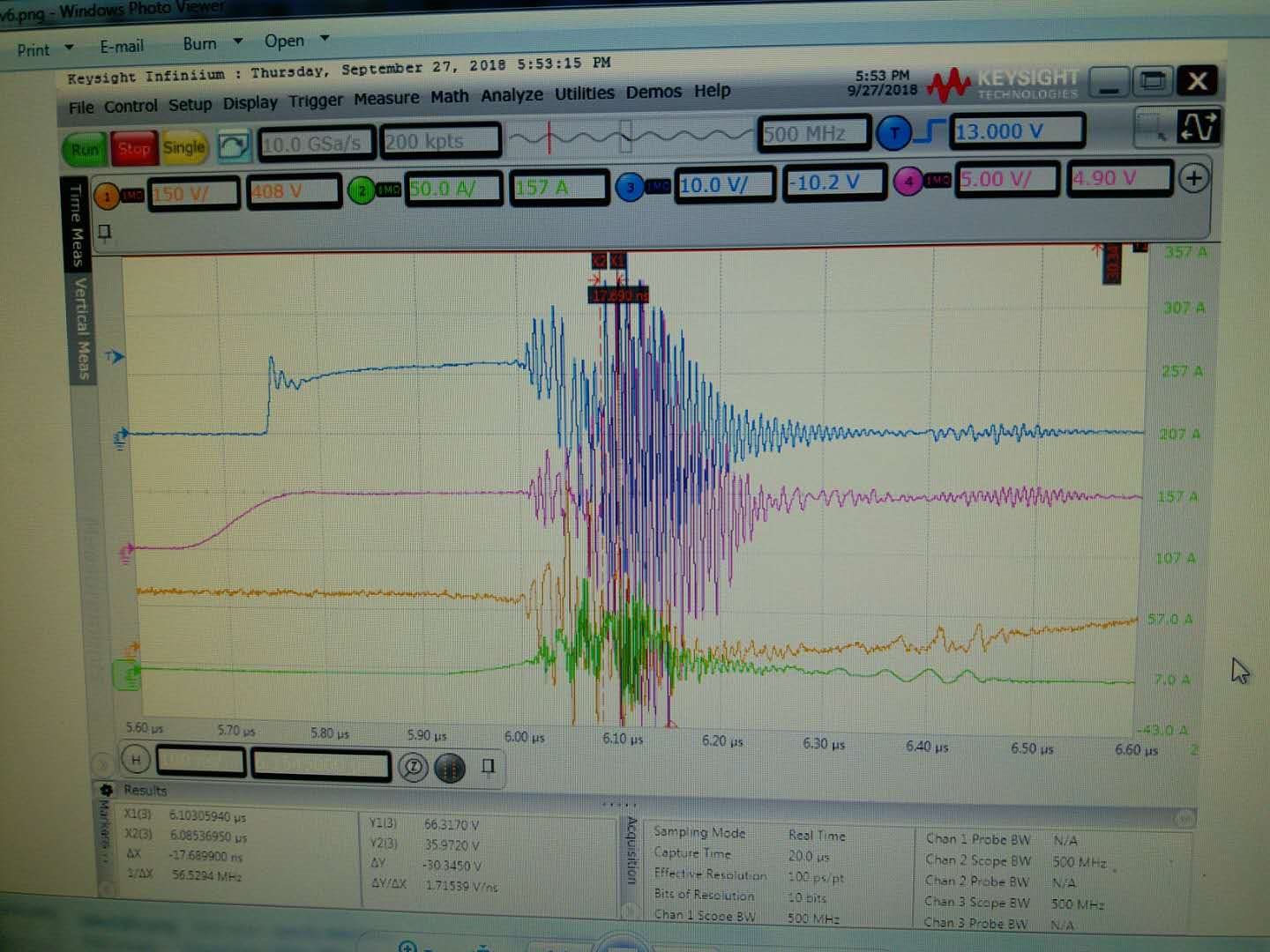

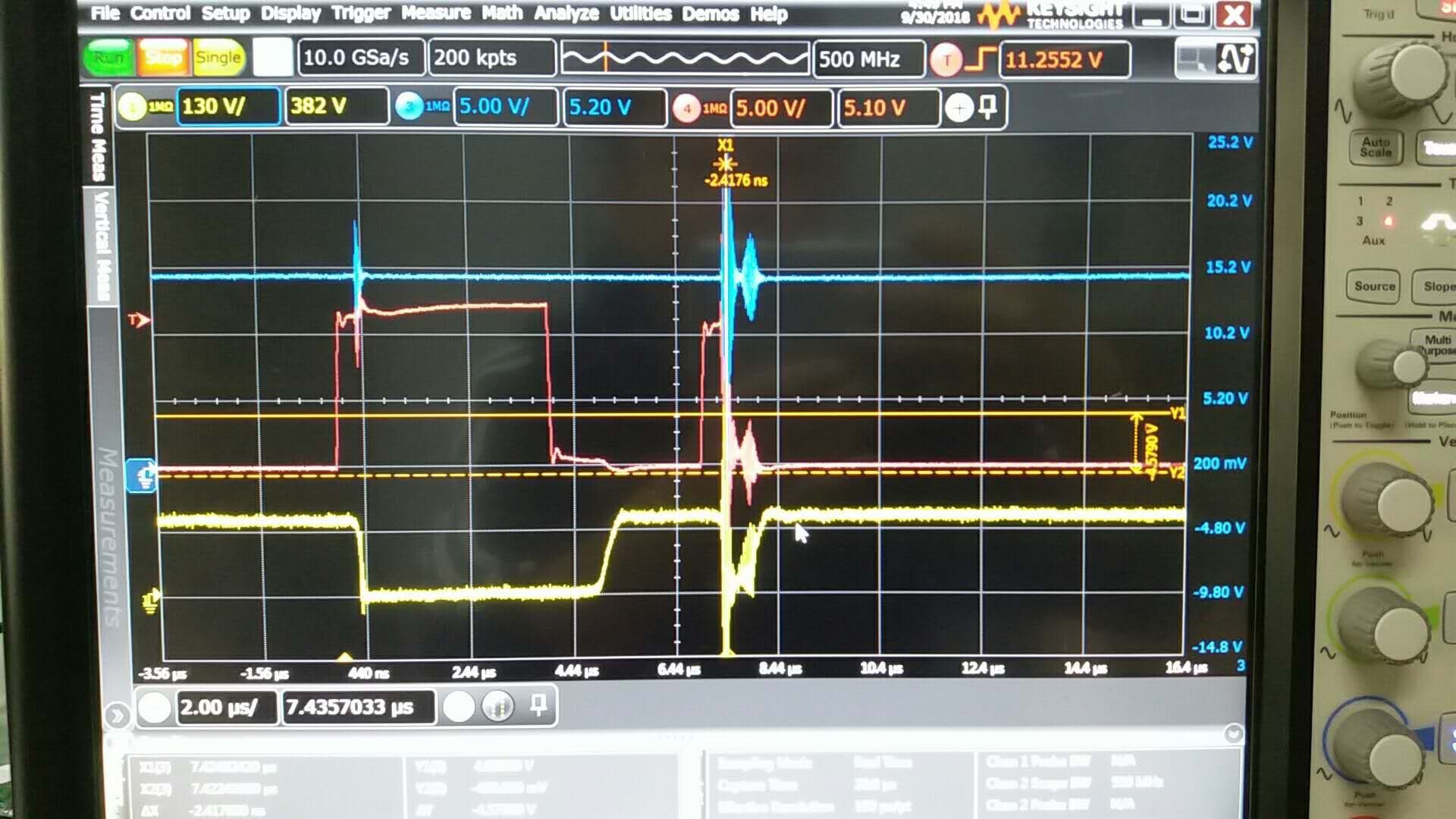

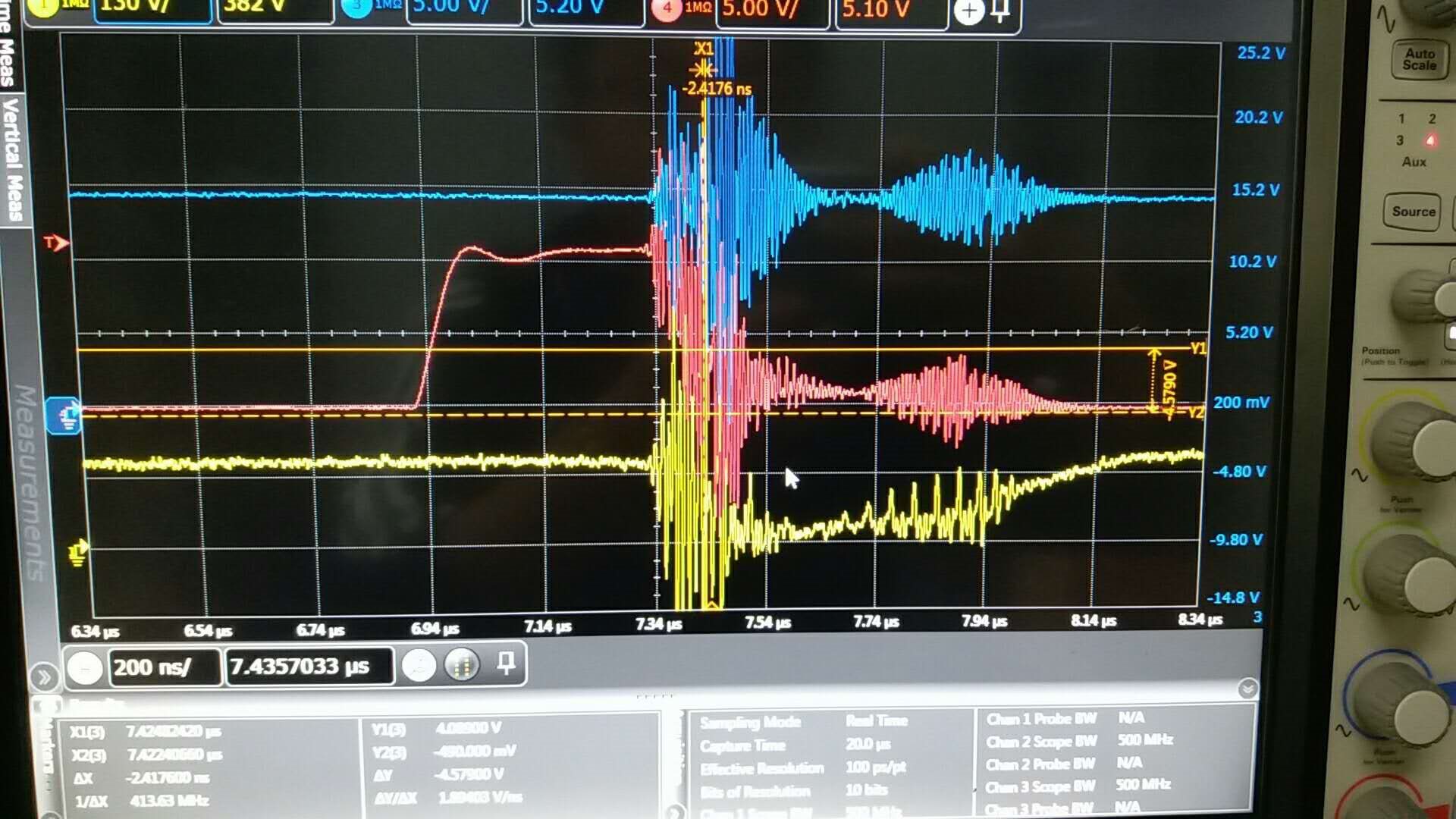

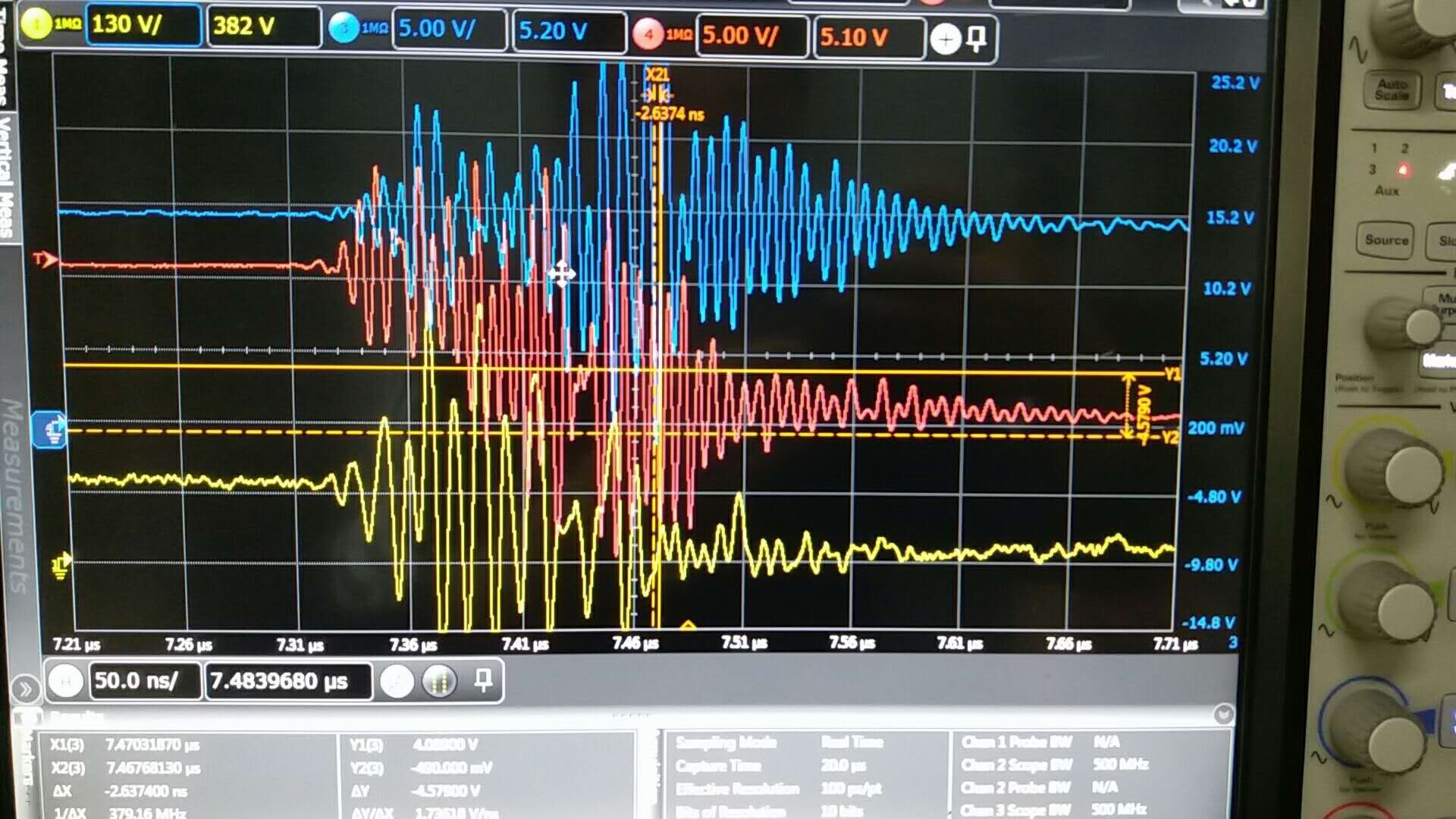

Zoom In at the event point:

I also asked customer to test the HB pin at the time of event. There are too many pictures. I will post the other pictures at the reply section.

Thanks

-Vincent