Other Parts Discussed in Thread: TPS65218

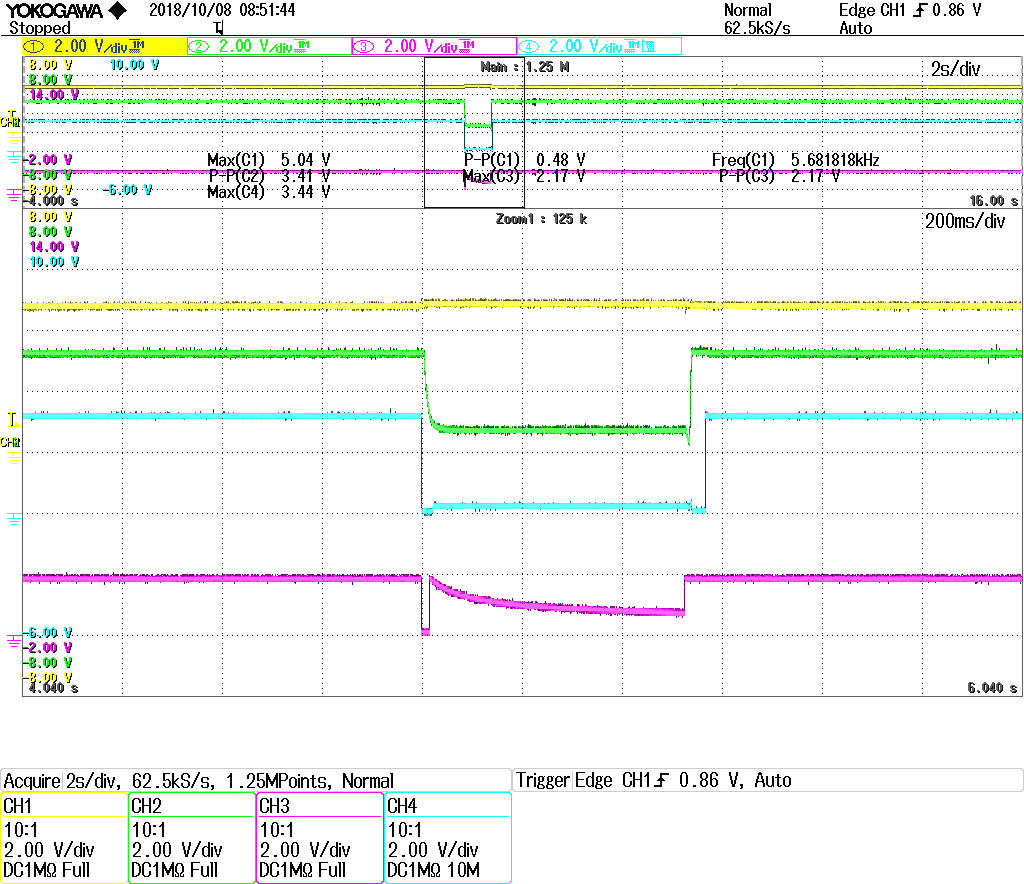

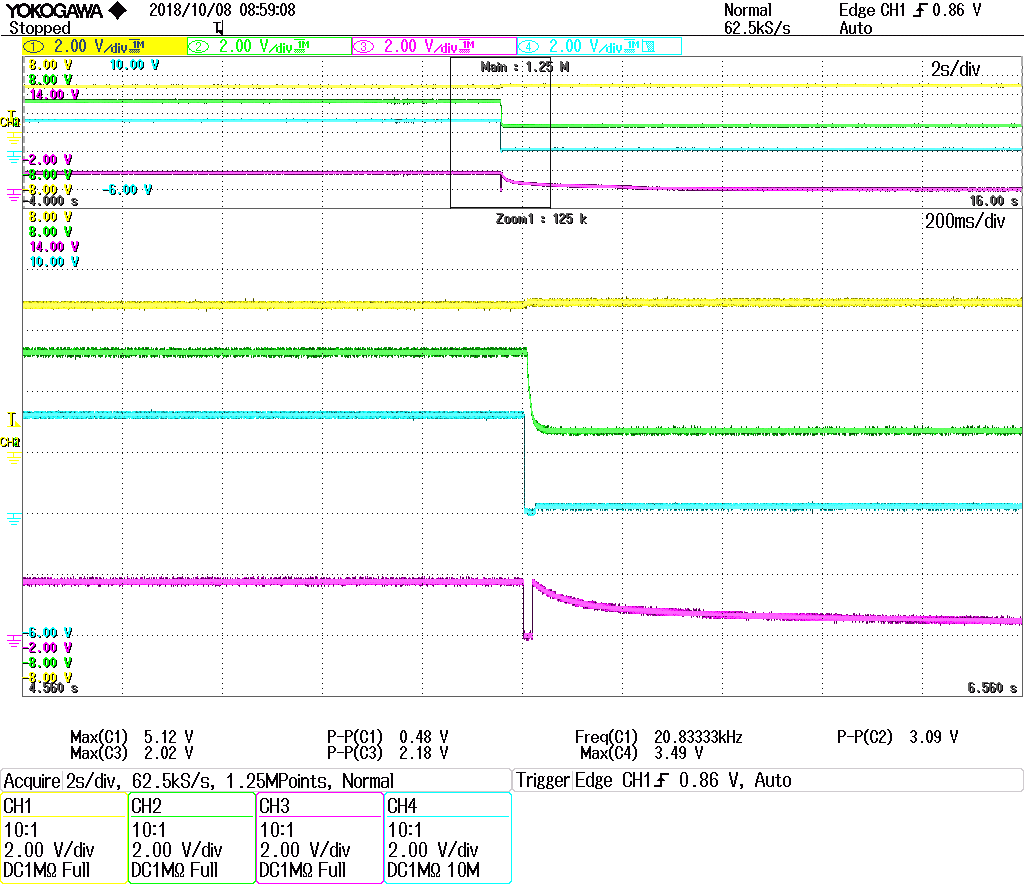

I have a different behavior if I send the poweroff command from my Linux System. With the former TPS65218B1 mounted on the same board the PMIC goes in the OFF state. The TPS65218D0 goes in the RECOVERY state (reboot after 500 ms). What could be the reason for this behavior? Is a new entry in the device tree required. My board is similar to the BeagleBoneBlack.