Hello there,

I am considering to replace the software watchdog with an external watchdog like TPS3828-33-Q1 in our design. I find the software one implemented in the MCU not so reliable.

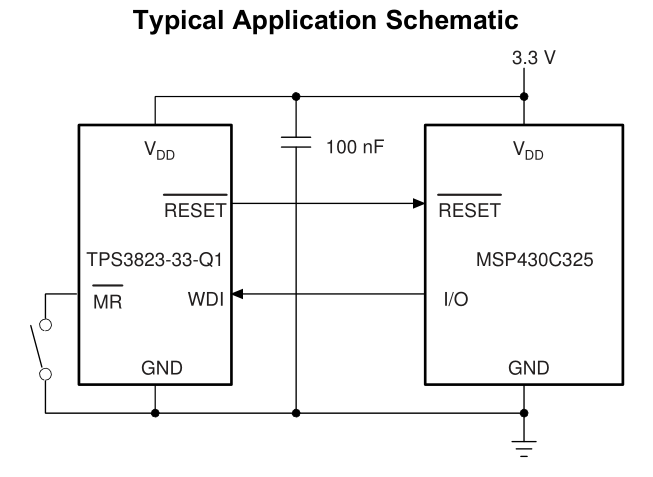

When thinking about this a question arises in my head. For example, lets cosider this example schematics from the datsheet:

Normally the #RESET line of the SWD/JTAG probe would be connected to the #MR line. The question is: what is the official way of handling this chip during software development or debugging? If I place a breakpoint in my code, that means the WDI signal will stop toggling, thus, the TPS3828 chip will reset my MCU... Since the probe is connected to the #MR line, not #RESET, I cannot really disconnect any circuitry for development. Seems like there should be an #ENABLE line available in the TPS3828 chip.I thought of multiplexing the WDI line with the probes CLK signal but that line is not always toggling (ie when stopped on a breakpoint and not reading anything), so this wouldnt work. On the other hand the TPS3828-33-Q1 model has open-drain as #RESET. In that case I could hardwire #MR to VCC and physically disconnect the #RESET line only from the TPS3828-33-Q1 chip (ie. using a jumpoer, N mosfet etc), leaving the probes #RESET line connected with MCU #RESET line. But this seems a bit of a hack than solution...

This one bugs me. I would appreciate all help regarding this issue.