Dear, Sir.

My customer is applying Infineon's High-side IPD like BTS5016, so I am considering

how to replace it to TI's product.

An engineer complained that Infineon's products don't reflect the advantage standing on

system level usage such as Reverse battery. I thought TI's product would meet with his

expectation, the replacement could be realized.

I am so sorry ask you about this kind of fundamental matter, but hoping to get your

teachings to improve my poor understanding.

1. Integrated Power FET.

Is it a NMOS FET?

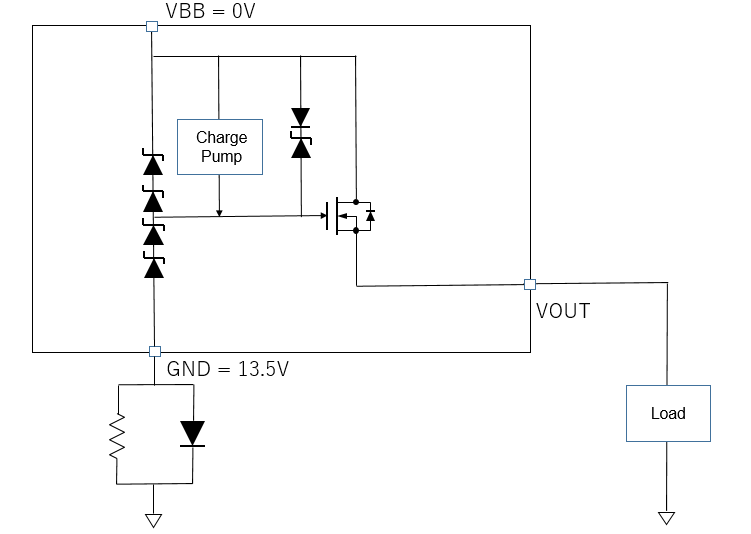

2. Internal Power Supply.

Is it a charge pump?

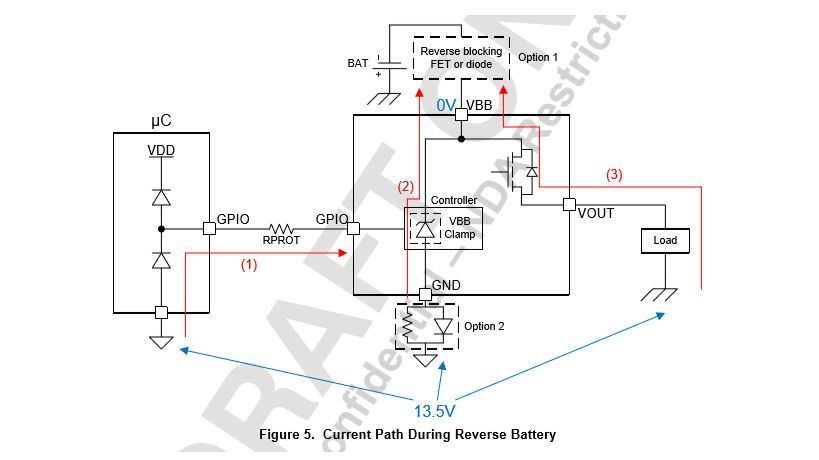

3. Automatic Switch On with Reverse Battery.

Does it mean TPS1HA08-Q1 can be driven FET gate under reverse battery condition

by biasing from GND side?

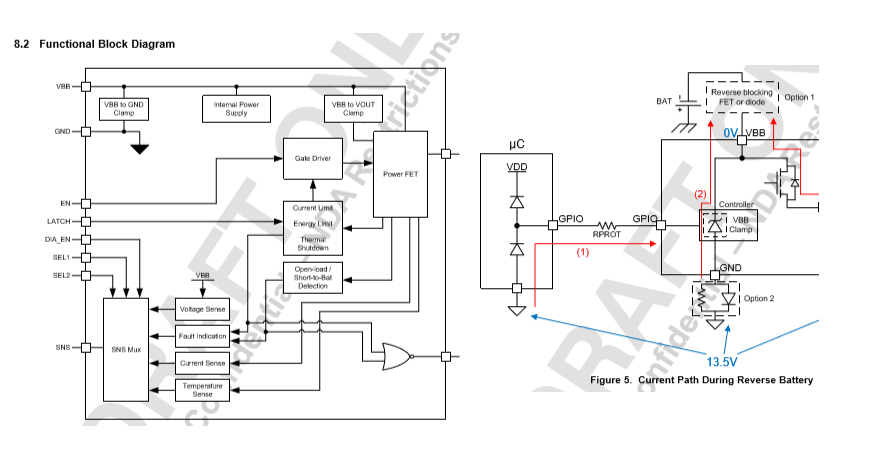

How to realize that utilizing function blocks? I checked 8.2 Functional Block Diagram on

DS, but not clarified yet.

Best Regards,

H. Sakai