Hi Experts,

While I was supporting one of our important customer, one important issue emerged. As the customer is using VR3 to generate a 3.3V output, which, has also been used as ENVR5 to enable VR5 when 3.3V ramps up. While I understood that the VRs were internally isolated and which pins related to VR3's output only included PGVR3, NVDCZ, VINVR3, ILIMVR3HS, ILIMVR3LS, FBVR3N, FBVR3P, VBSTVR3, DRVHVR3, SWVR3, DRVLVR3, PGNDVR3, ENVR3.

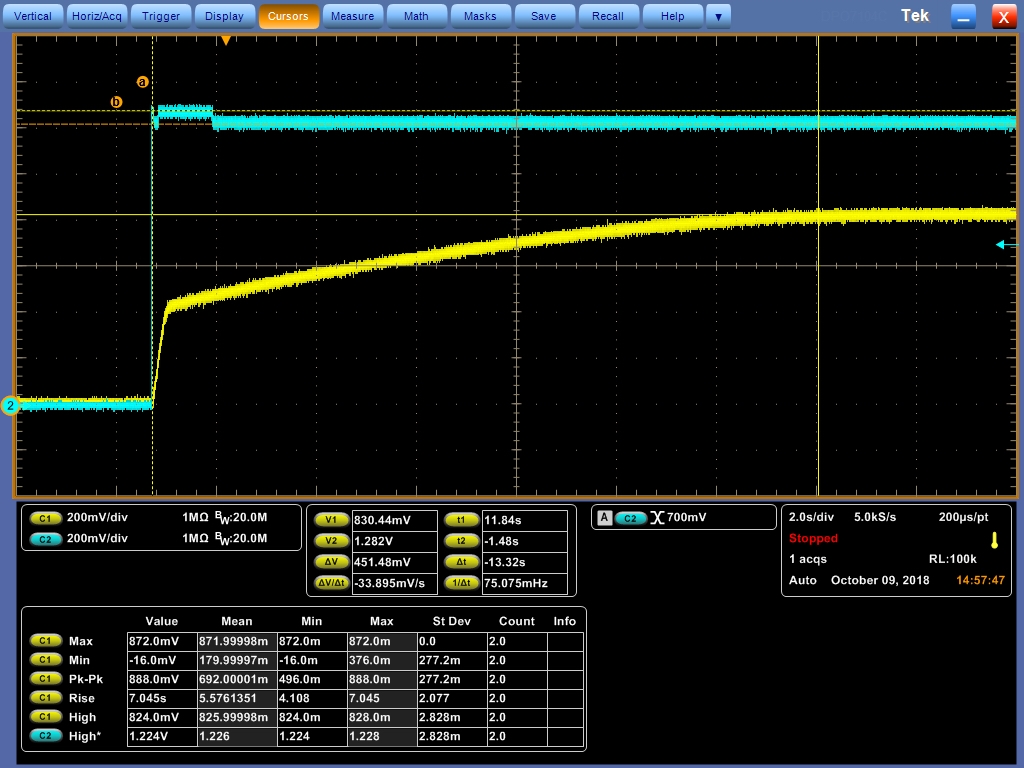

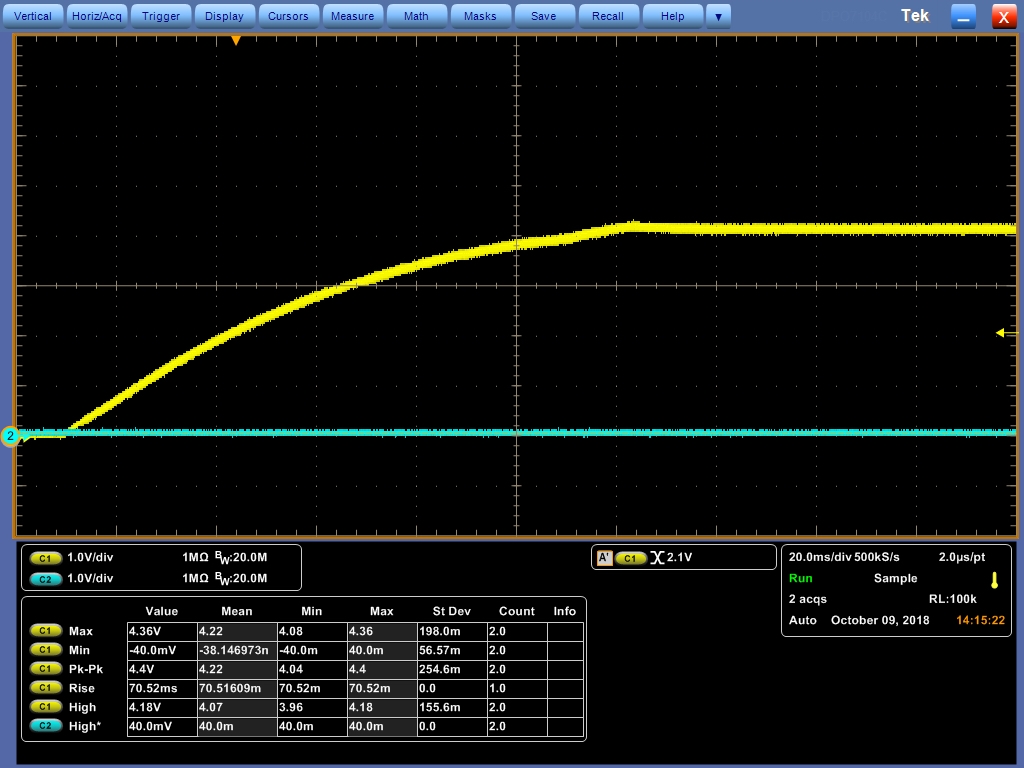

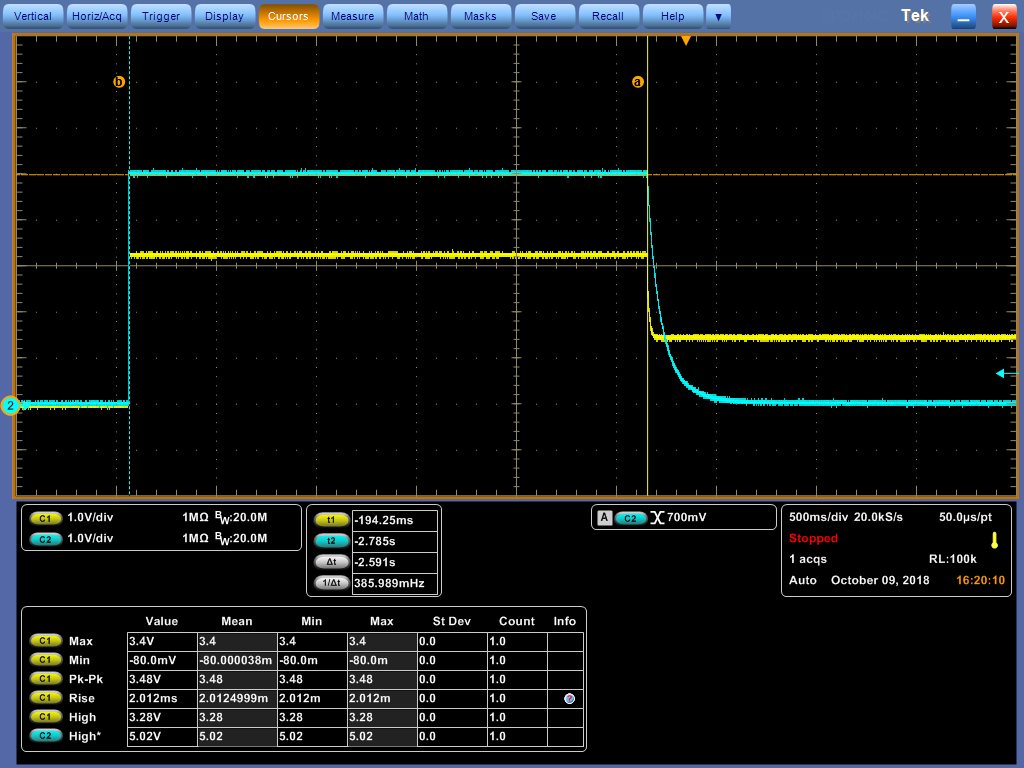

As the most critical pins that influence output are all above except PGVR3 and NVDCZ, the customer uses on-chip LDO3V to generate VR3's ENVR3 AND LDO5V to support VBSTVR3 and external 12V for VINVR3, VIN and VINLDO3, tending to make VR3 perform a 3.3V immediately after 12V powers on. However, 3.3V was not generated after power-on. While we were supporting them locally we found LDO3V had a really strange output shown as below and this issue happened randomly-> 16 pics in total, one of which LDO3V output is 0.84V and another output is 4.2V, note that all those 16 pics have totally same BOM and same layout. Those strange outputs have been suspected to be cause of making VR3 not output as 0.84V is too low to enable LDO5V and 4.2V is too large that might make internal logic disorder.

Note: Yellow line: LDO3V Output; Blue line VREF1V25 Output.

Note: Yellow Line: LDO3V Output; Blue Line: N/A

My question is,

1. What will cause LDO3V output unstably?

2. Merely from the waveforms, did those mean that two LDO3s do not work anymore?

Could you please comment this? Sorry by pushing you, but this is really emergent because they have been adjusting it for more than 30 days. Thank you for your great help!

-Wenhao