Dear all,

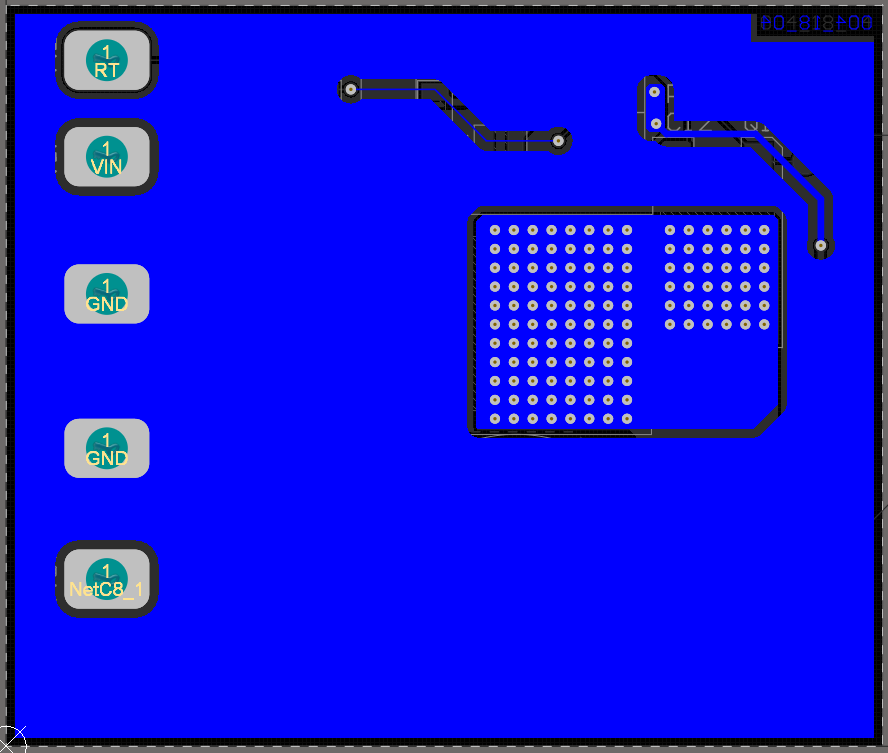

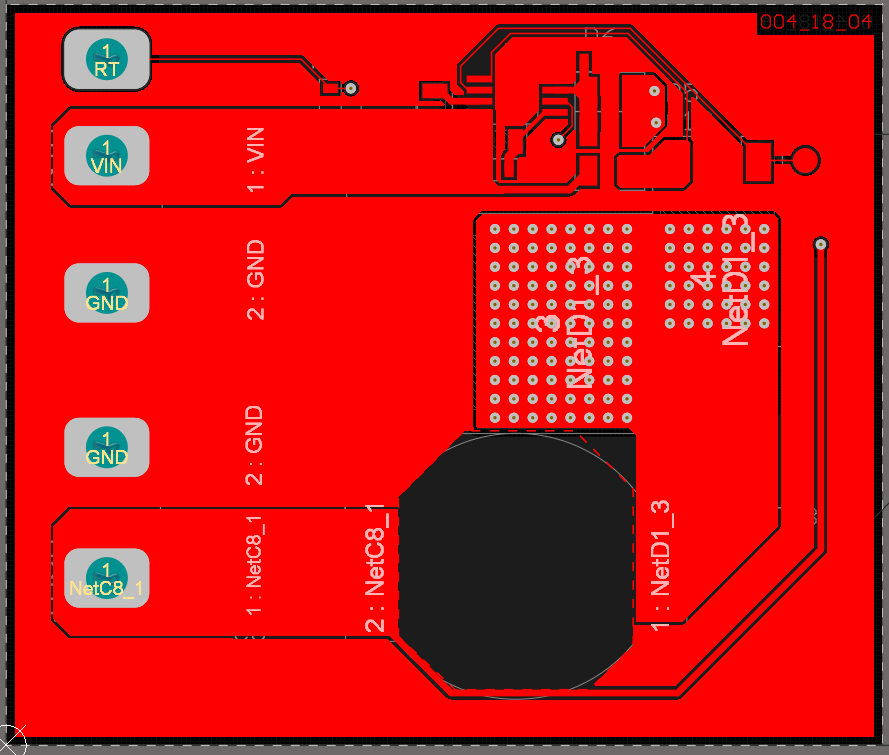

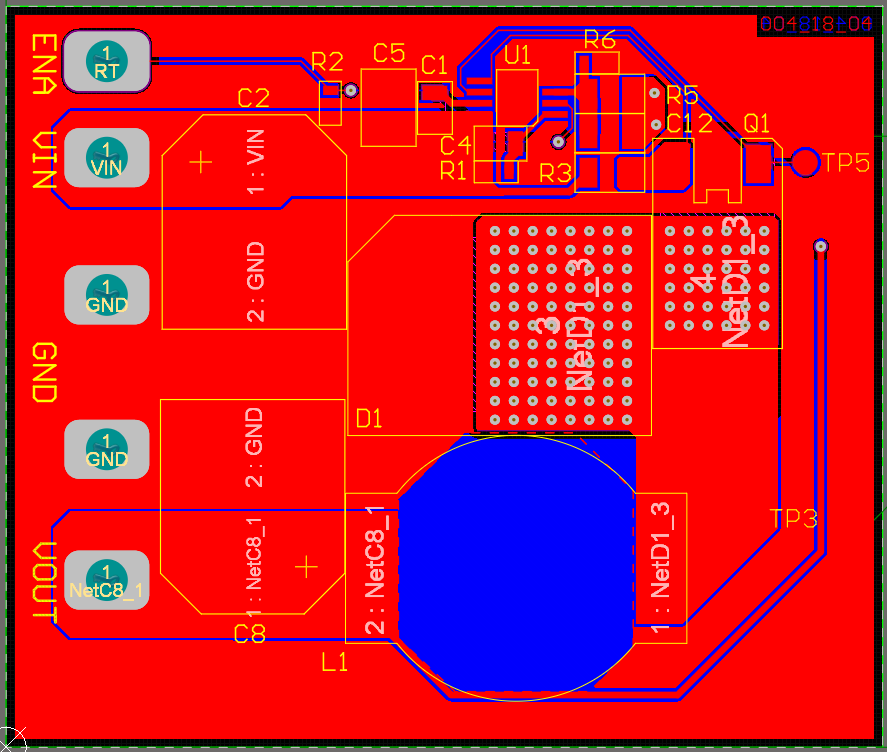

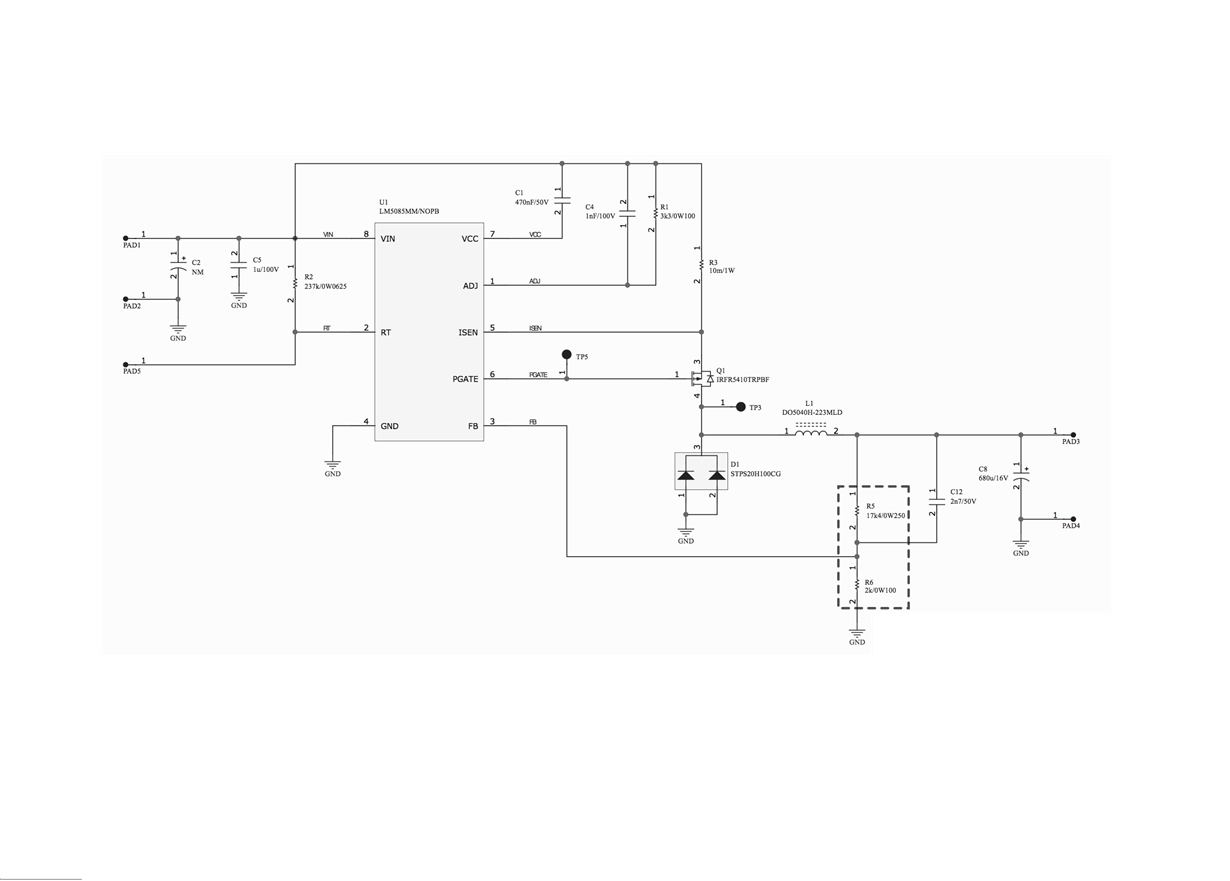

In my last post: LM508 does not work for V_INPUT below 35VDC I had problems with EMIs for IOUT >5A. I've modified the layout by moving the controller far from the position of the SW node and at the same time I've reduced the area of the SW node as much as possible.

By doing this I've achieved to have uo to 7A at the outpout. However, for higher values my DCDC starts to work erraticaly, tha PWM frequency decays up to 20-30kHz, VOUT is 0.72V and the output current is 6.5A when my DC-Load is configured at 10A. I really believe that I stilll having EMIs issues, I've attched my layout.

I plan to increase the number of layers up to 4 and to place GND vias close the edge of the PCB, do you think with both I'll have enough to reduce the EMIs drastically?

Many thanks!

David