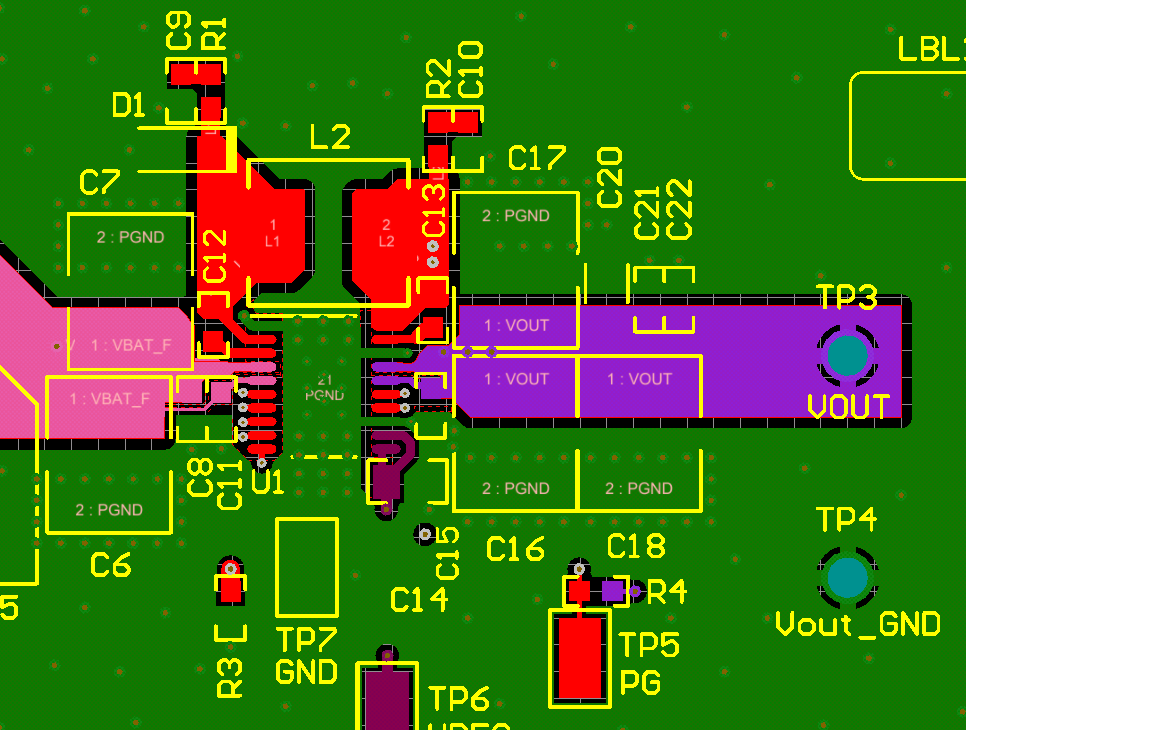

I've got the TPS55165 on a PCB. Input range will be 8 to 18 V. Output voltage 12V, current needed is 320 mA max, 120mA typical. 2 sided board, bottom is ground plane. All cap values as per the data sheet. When I turn it on, I get anything from 3 to 10 volts out. Sometimes I have to change the input voltage up and down before it gets to 10V. I increased the caps on VREG up to 6.8 uF with 3 ceramic caps and 2 x.1 uF. Output C is 2 x 22uF with a .01 and .1uF. Input C is 2x2.2uF, a 15 uF tantalum, a .1 and a .01uF. IGN is high, PS and IGN_PWRL are low. PG_DLY goes to ground (tried to VREG, no change). Sometimes on power up PG is high (100K to +5 Pull up), sometimes it stays low. The layout is similar to the one shown, it's all very tight with a ground plane.

Bottom line, I can not get it to output 12V under any condition. Any ideas on what to check? If not, I'll try some different part since I can't risk something this fussy in a production environment.

The data sheet is not the best I've seen from TI. I'm not sure what is meant by the IGN_PWRL being called the "latch". I've going by section 8.4.3 and figure 16 in the data sheet which imply that you can just pull up IGN (I have 1K to +5) and ground PS and IGN_PWRL. I just want it to turn on and stay on (no low power) on power up. What ever I use next, I'll cut a test board first (this is on the first proto of the entire system). It really should be as simple as put on the passives and get 12V out.