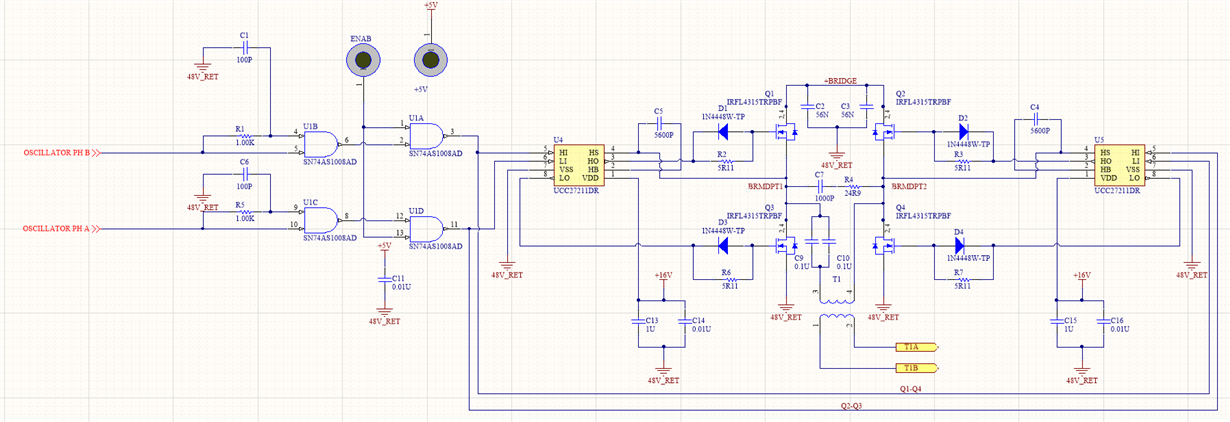

Part Number: UCC27211

Hello,

I apologize for taking so long to respond. I had to attend to another project.

The problem remains after replacing the 5600 pF bootstrap capacitor with a 0.1U capacitor.

The problem is intermittent. I can replace the chip and it will operate without issue several times. Somewhere between the 2nd and 10th power-up, my 48V bus drops to 3V as my power supply goes into current limit. IR imaging shows that the UCC27211DR is well over 90C case temperature in less than 3 seconds after power up. The chip is fried as the board cannot be recovered until the chip is replace. This isn't a "one off". I have 10 boards with the exact same problem.

I will replace the chip today and take scope data. In the meantime, do you have any other suggestions?

Thank you.