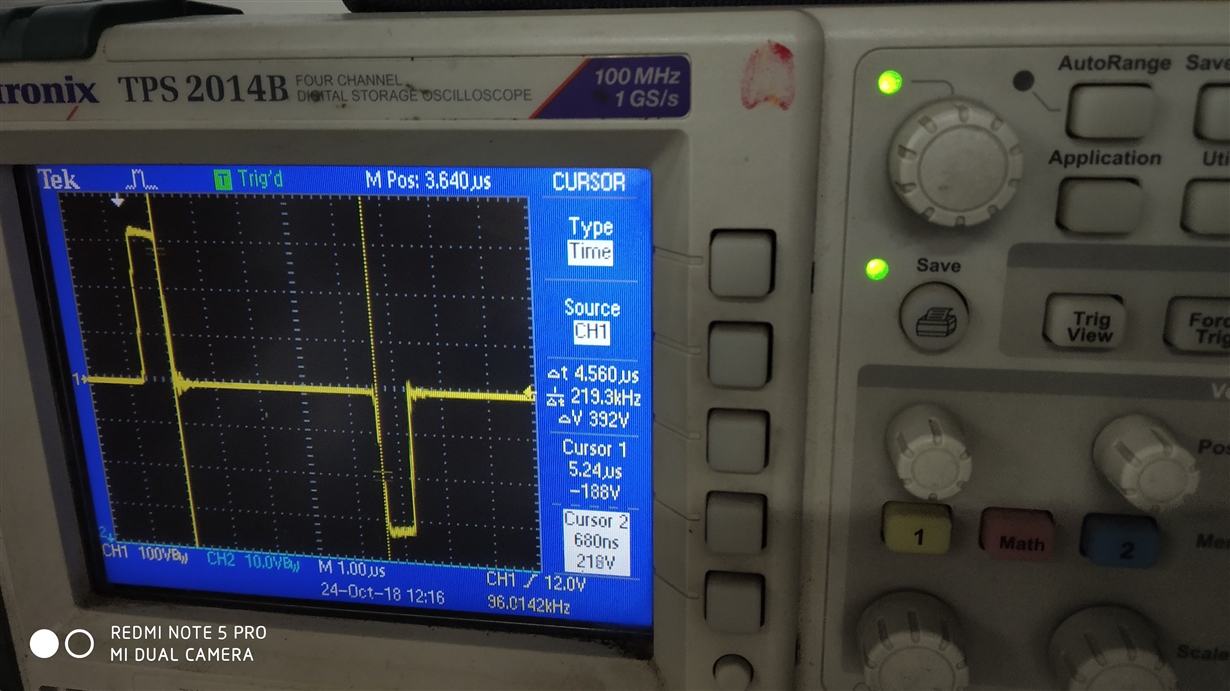

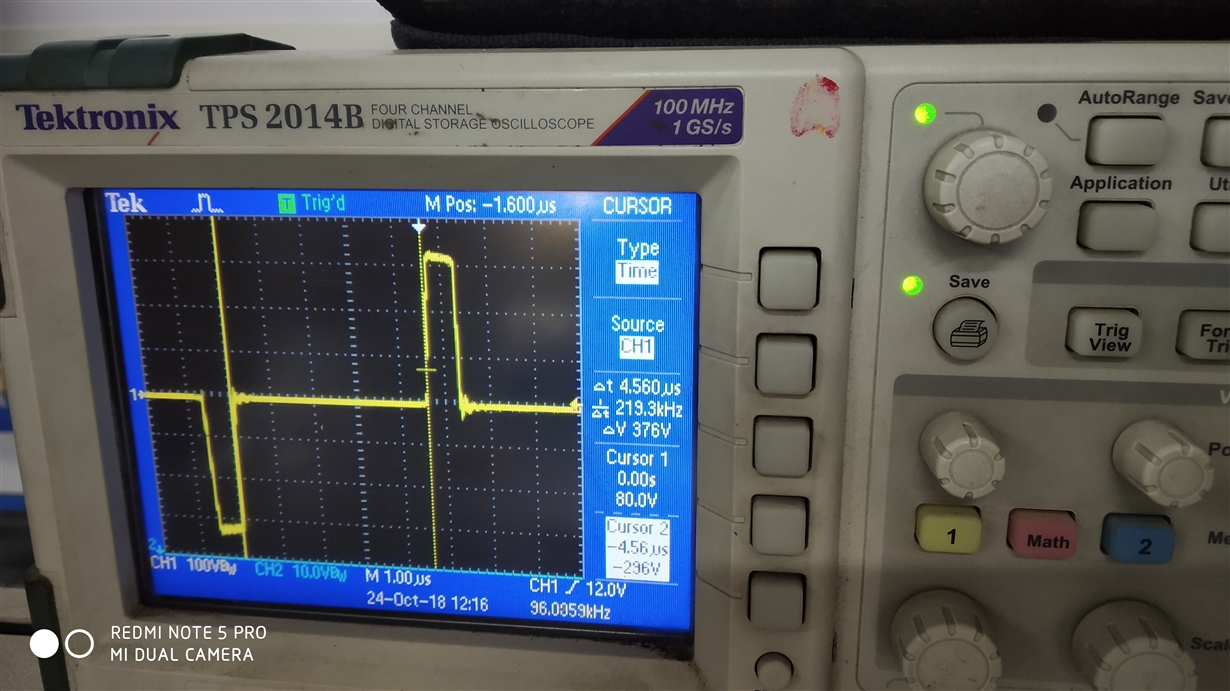

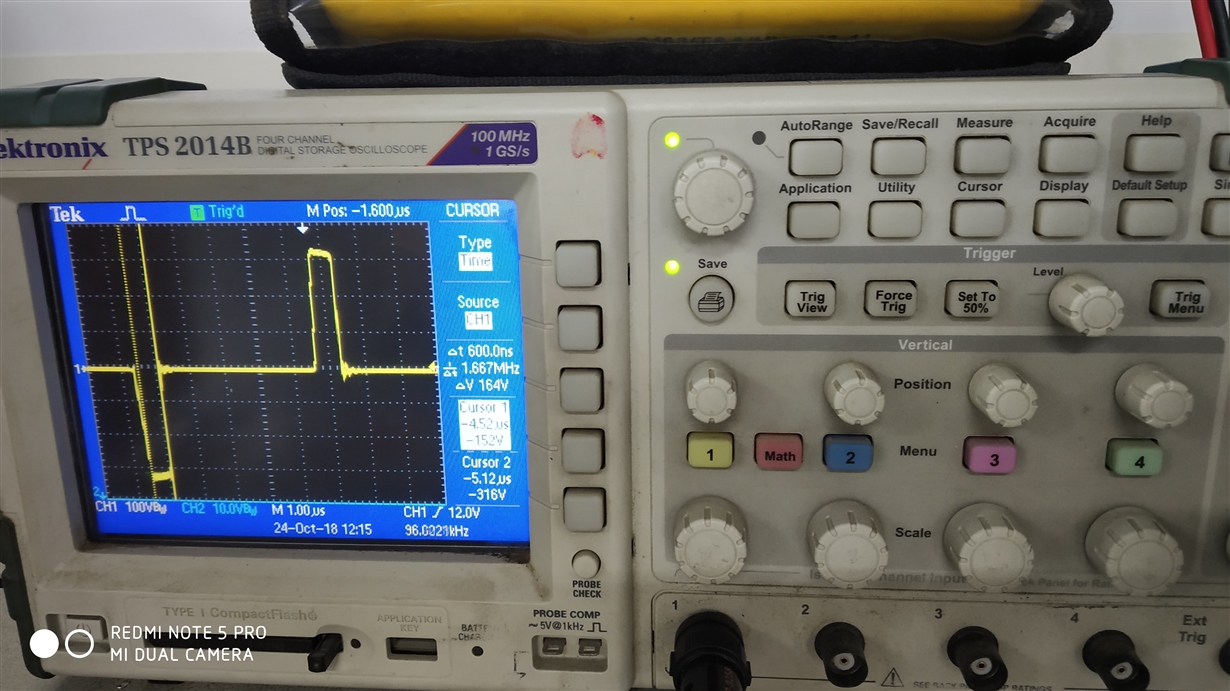

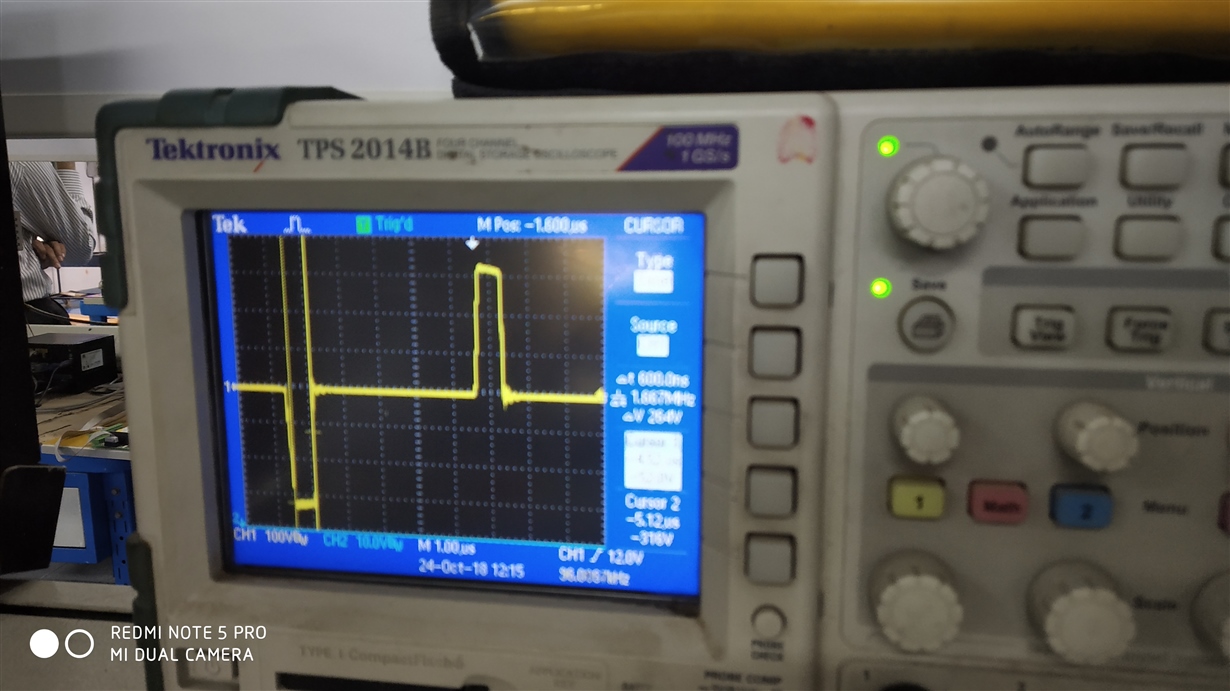

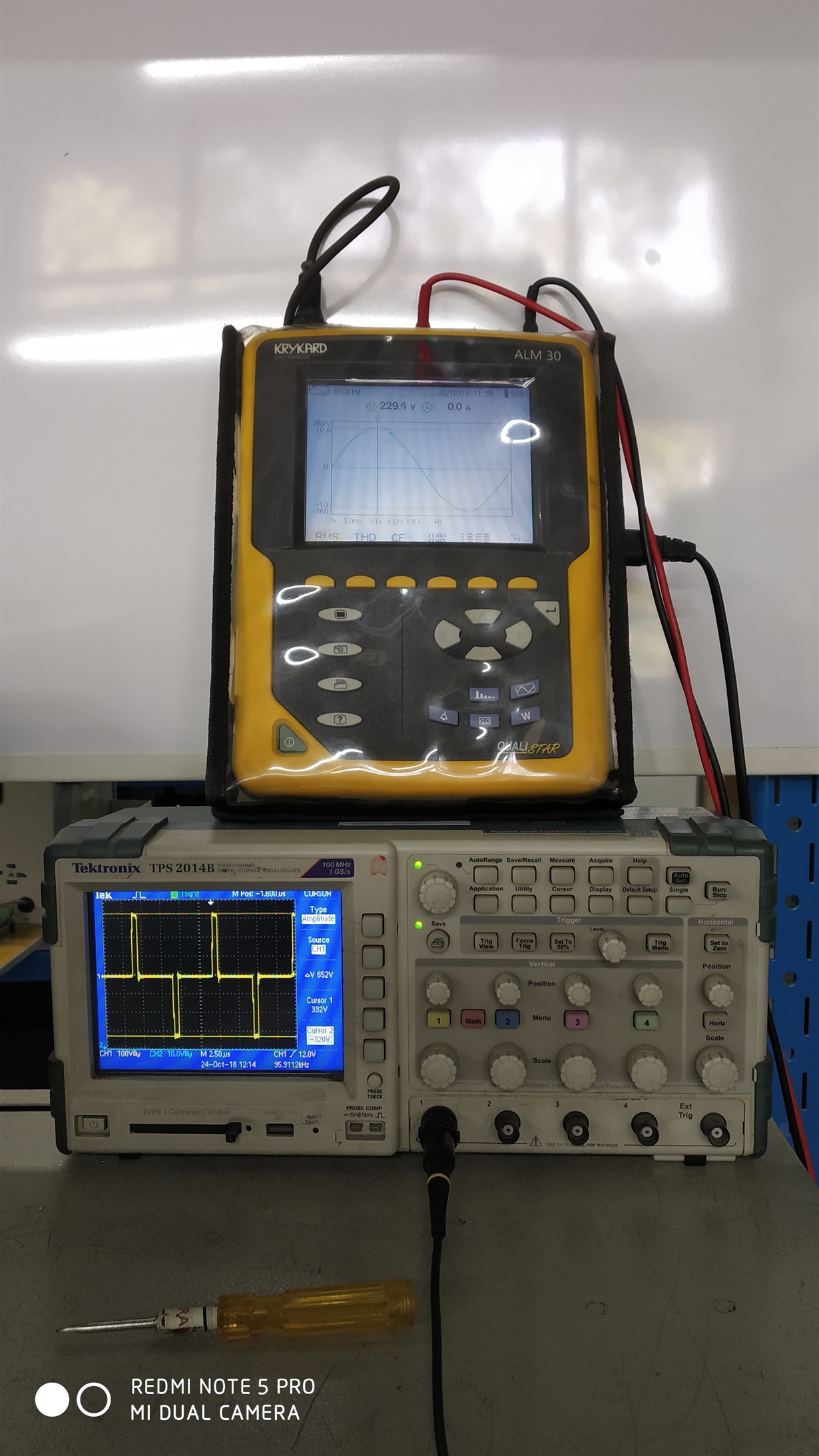

Correct.. . today i tested DCDC at no load and power-up through rectifier+ 330uF/450V capacitor. I am attacheing waveforms of transformer primary at no load. also i got stable output voltage of 53.9V at output of DCDC converter. After this i tried to load 1.5A current (37.5Ohm Resistive load) but output get reduced to 3V -1.5V , but if i disconnect the load then output voltage recovered to 53.9VDC.

Is this because of my voltage control loop?

My transformer is PQ50/50, Primary1: 8Turns, Secondary1: 3Turns, Secondary2: 3Turns, Primary2: 7Turns .

Thanks,