Other Parts Discussed in Thread: TINA-TI

Tool/software: TINA-TI or Spice Models

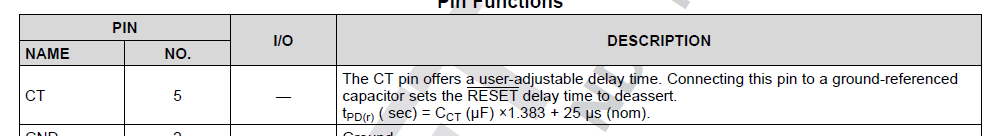

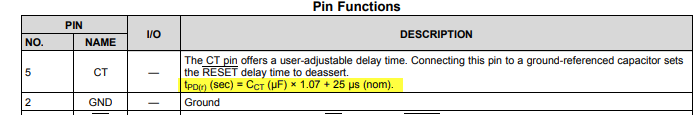

I am doing the the simulation in TINA with TPS389012 and TPS389033 to monitor multiple supply voltages of 1.2 and 3.3 as shown in the page no. 12(figure 23) of the data sheet. Spice models are taken from TI website.CT capacitor of 0.1uf (gives around 100ms delay) is put for bith the chips. 10K pull up is used at both chips reset pin. both 3.3 and 1.2 volt have slew time of 20ms.

when transient simulation is done the delay b/w MR(at 3.3 volt) and reset high of the 1.2 monitoring chip(TPS389012) is coming around 100 ms, but the,delay between MR high to reset high for the 3.3V monitoring chip(TPS389033) is only 5ms, which is not correct as per the data sheet(it should be ~100ms). Kindly help me out to solve the issue. Is it because spice model is not taking in to account of this case.