Dear Sir,

We found the VCCIO & PVCCIN turned off delay time was too long issue, causing short circuit of processor FIVR.

Is there a way to adjust the turn off shunt down rate(mv/us) with the GUI?

Thank you!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear Sir,

We found the VCCIO & PVCCIN turned off delay time was too long issue, causing short circuit of processor FIVR.

Is there a way to adjust the turn off shunt down rate(mv/us) with the GUI?

Thank you!

Pin 13 of TPS53659 is u dual function pin. The default is to be an enable pin for Channel B. You may also configure Pin 13 to be a VCCIO Undervoltage monitoring pin. This selection is under MFR_SPECIFIC_00.

When the TPS53659 detects VCCIO undervoltage, it will ramp the output voltage down actively to 0V at the rate specified by SetVID-Slow.

Dear Sir,

When Pin 10 (AVR_EN) drop before Pin 13 (connect to VCCIO), we found channel A output still can not shutdown rapidly, ever through VCCIO drop under 0.65V.

But when Pin 10 keep high and Pin 13 drop firstly, Channel A output can shutdown rapidly.

Is these the right reaction?

Dear Sir,

After experiment, VCCIN can drop rapidly when "AVR_EN" keep high and "BEN_VCCIO" drop, but if "AVR_EN" drop before "BEN_VCCIO" drop, VCCIN will shutdown slowly,.

Is it the right action? In the normal system sequence, "AVR_EN" always drop before(or the same time) VCCIO disable. We have tried connect "PG of VCCIO" to "AVR_EN" and "BEN_VCCIO" to "VCCIO", but this connection still can not let VCCIN drop rapidly. Is there a suggested setting method?

In addition, Here are two bring-up problem needs help.

1. VR13 rail power down slew rate:

According following Intel requirement, PVCCIN may need controlled ramp down rate. Could you help to confirm this feature?

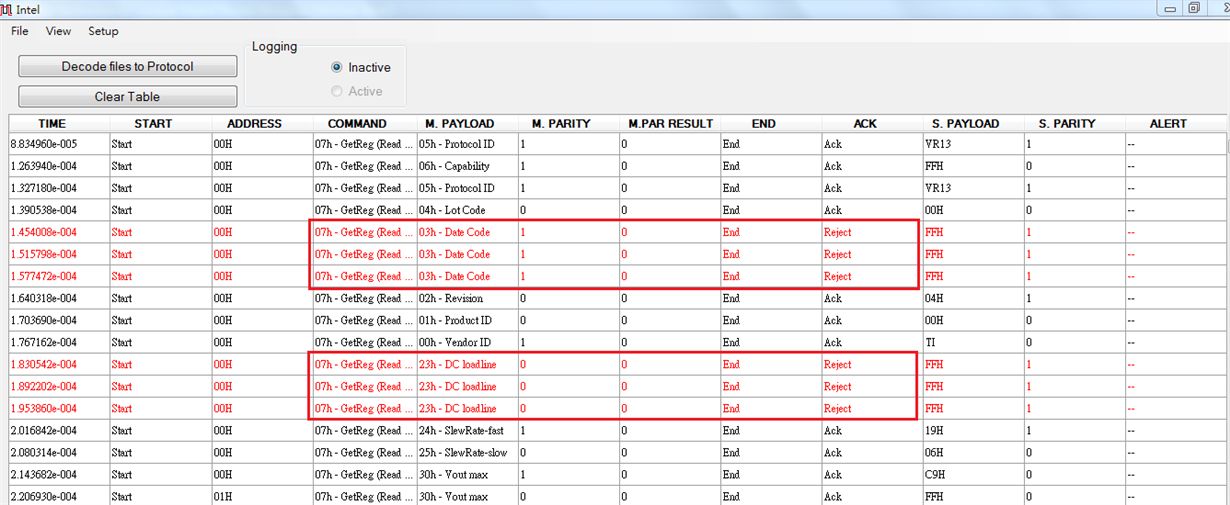

2. We decode SVID comment and found two register can not be read from VR13 controller: "03h data code" & "23h DC loadline".

Are these two register available and necessary?

Thank you!