Other Parts Discussed in Thread: UC2843, UCD3138

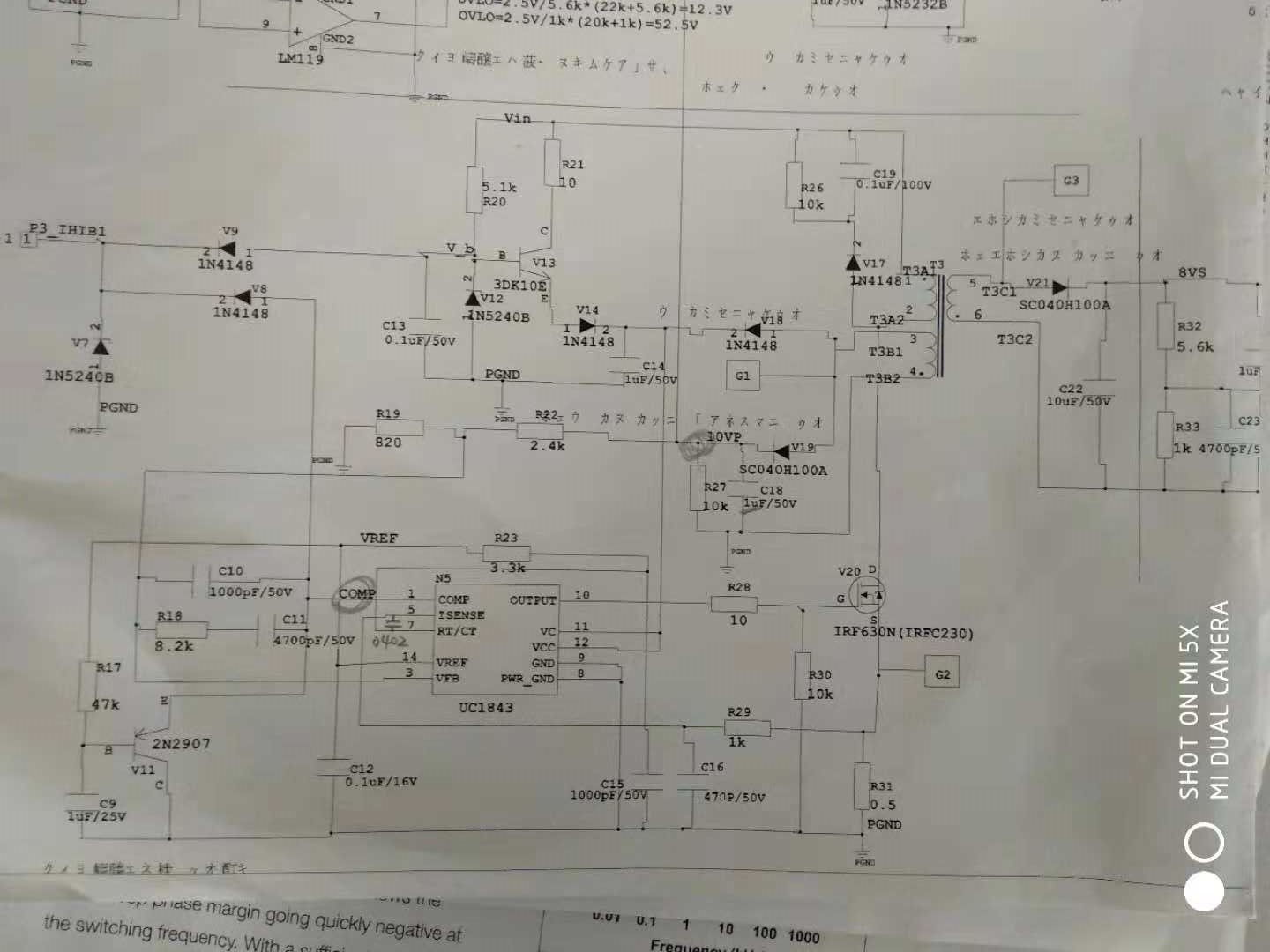

I made a flyback circuit based on UC3843.

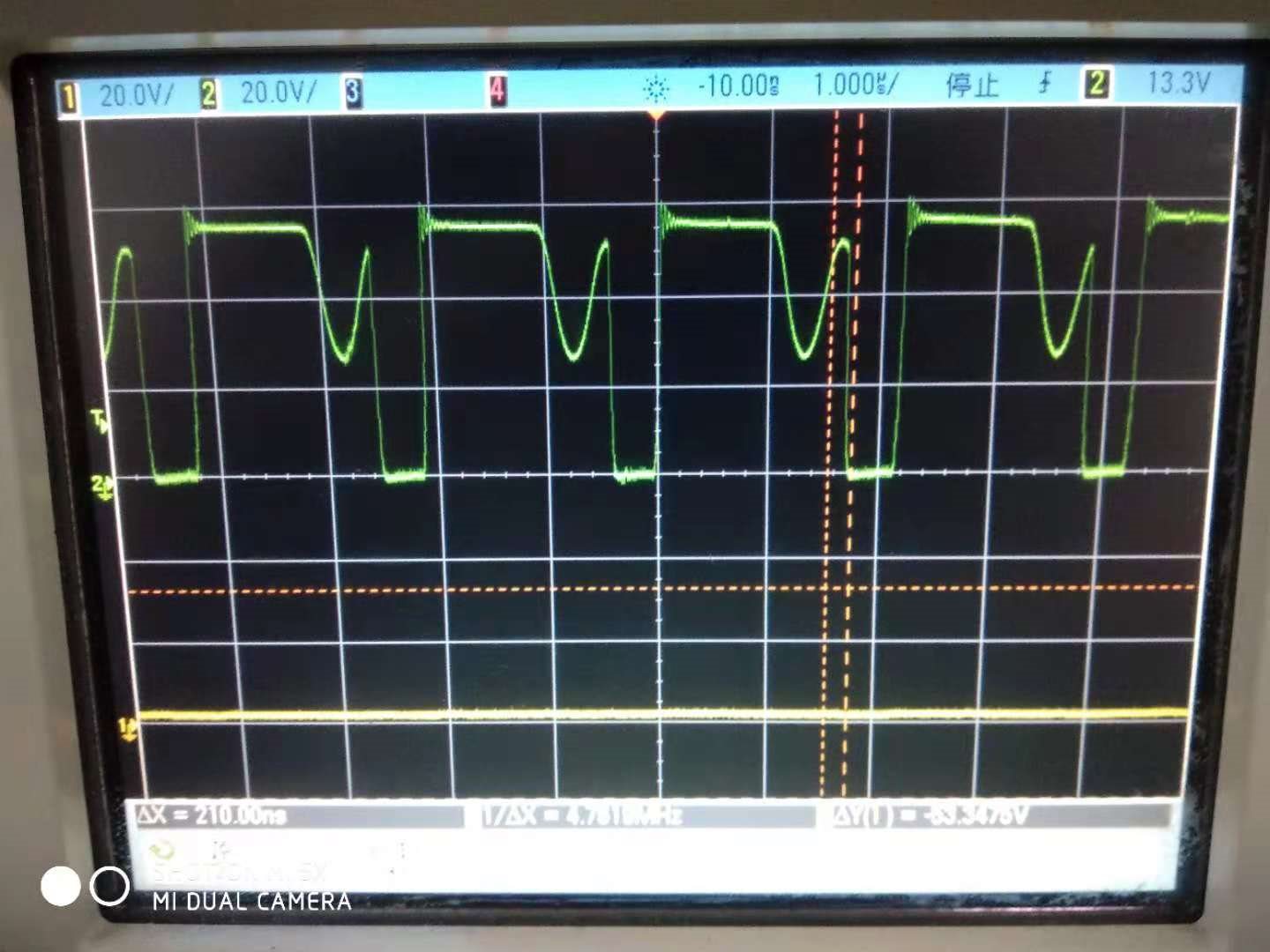

When the input voltage reaches 40V, the duty cycle is unstable, and the phenomenon is suddenly large and small, which varies between 0.2 and 0.25.

As shown in the figure below, the MOS tube drain source Voltage waveform.

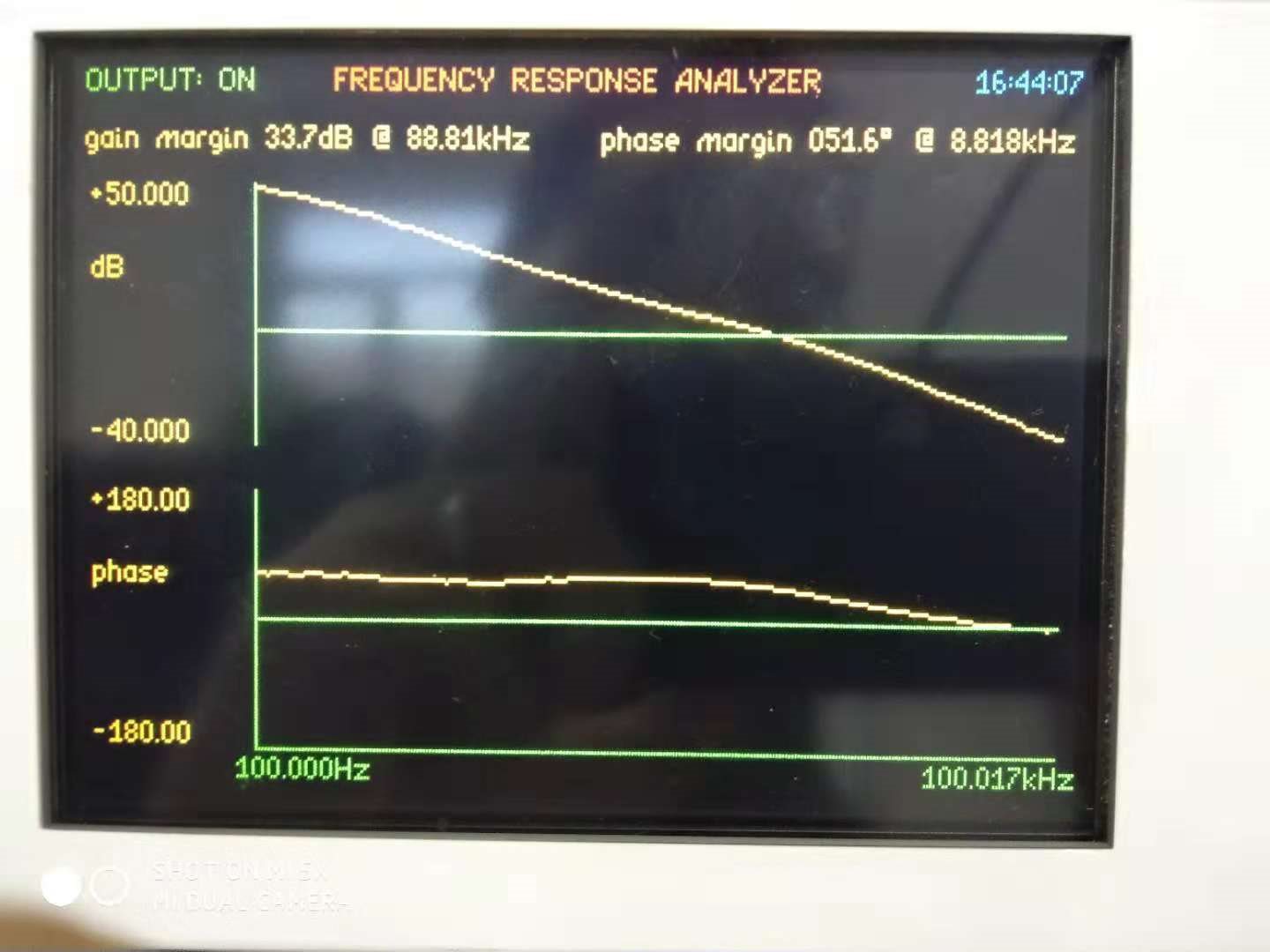

我测试了此时的伯德图,如下图:

At this point, the phase margin is 51 degrees and the gain margin is -33dB. The loop parameters are still quite good.

I don't know what caused this? The loop is stable, but the actual drive wave D is unstable.