Other Parts Discussed in Thread: PMP20878, TPS2373,

Hi team

My customers referenced the PMP20878 to design a PoE 802.3bt PD circuit.

In the PMP20878 circuit, they changed that L6 is connected directly, and C46 is changed to 22uF*2ea.

At setting above, I have seen waveform that skipped pulse as follow when power on.

[ Ch1(Yellow) : TPS2373-VC IN / Ch2(Blue) : UCC2897A-VDD / Ch3(Pink) : Vds for Q16 / Ch4(Green) : UCC2897A-FB ]

So, they changed C46 to 10uF.

When it did so, does not have event that that skipped pulse as follow when power on.

[ Ch1(Yellow) : TPS2373-VC IN / Ch2(Blue) : UCC2897A-VDD / Ch3(Pink) : Vds for Q16 / Ch4(Green) : UCC2897A-FB ]

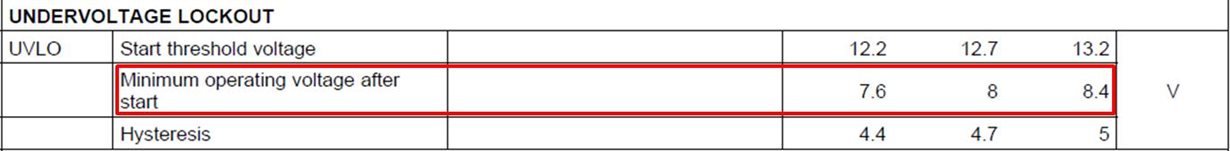

The VC-OUT voltage of the TPS2373 is higher than UCC2897's minimum operating voltage of 8V.

Please describe the reason why it works as above.