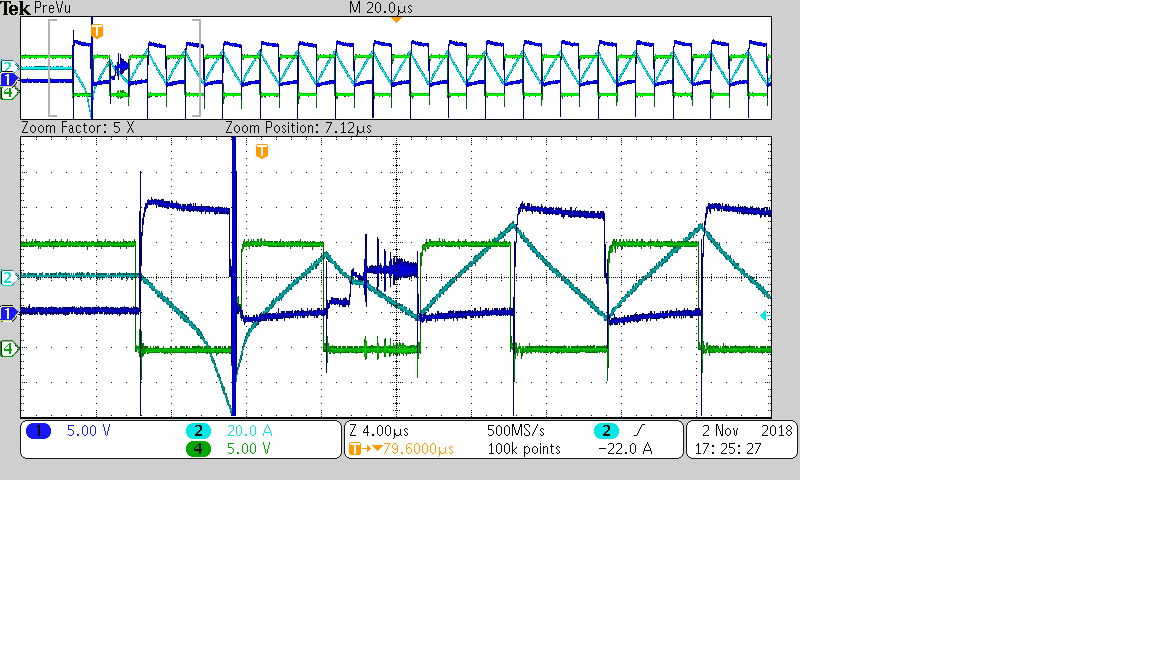

I am using two of these driver to drive one side of a dual active bridge converter. I am experiencing a glitch in the high side output when first turning on. I've checked the VDDA and it is steady at 15V with small 1/4V to 1/2V dips. There is a good amount of noise during startup but I would like to know the nature of this behavior to try to find a patch. All rails have been up for several seconds prior to enabling the driver.

INA/INB RC = 51 Ohms + 220pf

VDD1 = 3.3V with 0.47uf and 0.01uf

ENABLE pin RC = 51 Ohms + 220pf

CH1(blue): High side output

CH2(light blue): Inductor current

CH4(green): Low side output