Other Parts Discussed in Thread: UCD3138

Hello

I recently designed a 200W full-bridge switching power supply prototype based on your UCD3138 full-bridge hard-switch development board.

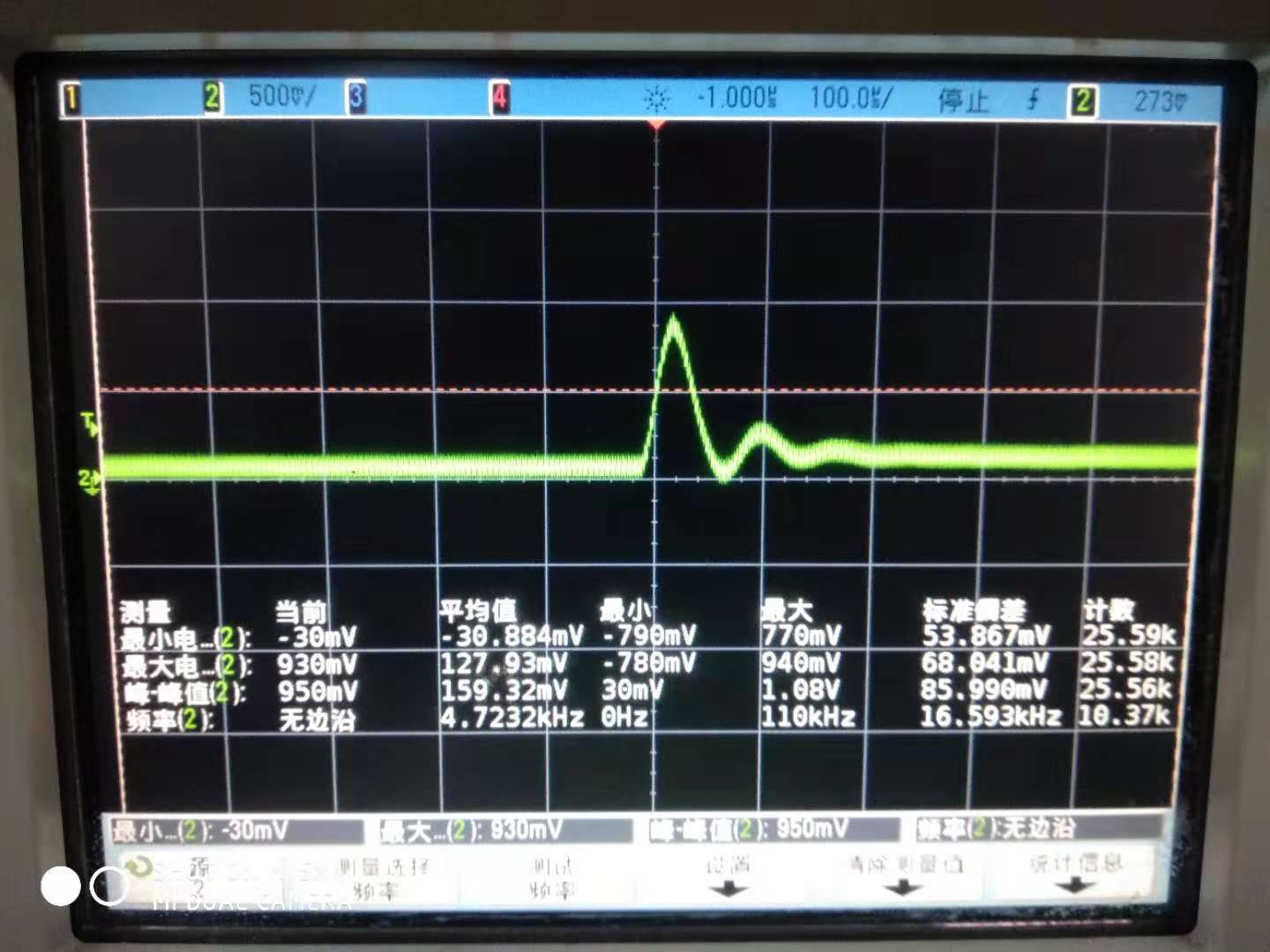

I tested the load step of the prototype I designed. The load jumps from 20A to 40A, then from 40A to 20A, the transition time is 10us, and the transition rate is 2A/us.

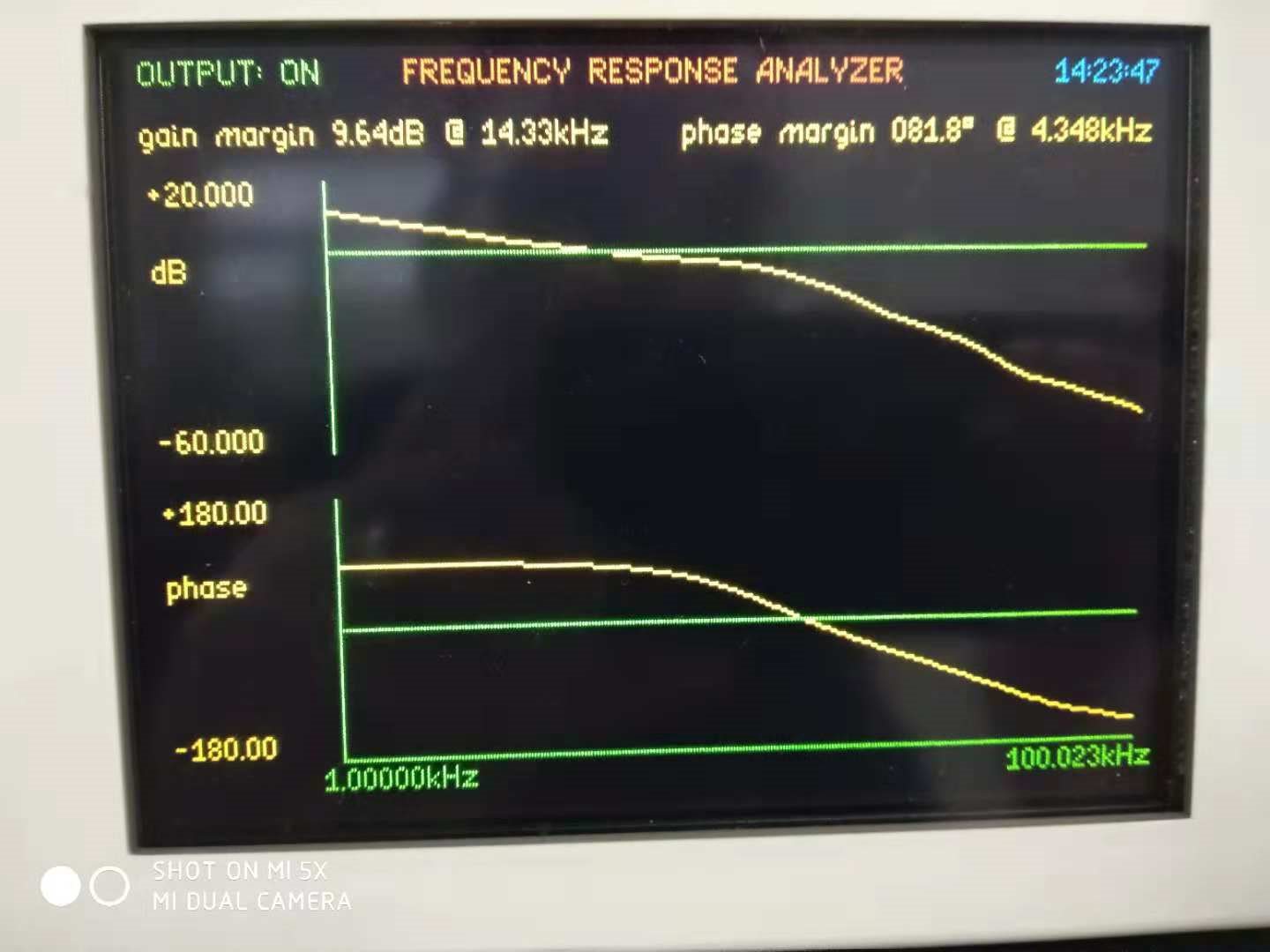

When the Bode diagram bandwidth of the prototype is 4.3 kHz, the amplitude of the overshoot and the amplitude of the sag are about 900 mV when the load jumps.

I optimized the PID coefficient and increased the bandwidth to 10 kHz for a load jump.

I thought that both the amplitude of the overshoot and the magnitude of the sag will decrease when the load jumps. However, strange things happened.

The load jump is that the amplitude of the undershoot drops to 410mV, while the amplitude of the overshoot does not change substantially, is 930mV. Why?

I thought that the bandwidth will increase, the amplitude of the overshoot and the amplitude of the undershoot will decrease.

However, the overshoot has not changed, I really can't understand.

How can I adjust and reduce the amplitude of the upper and lower amplitudes? Can only increase the output capacitor?