Hi,

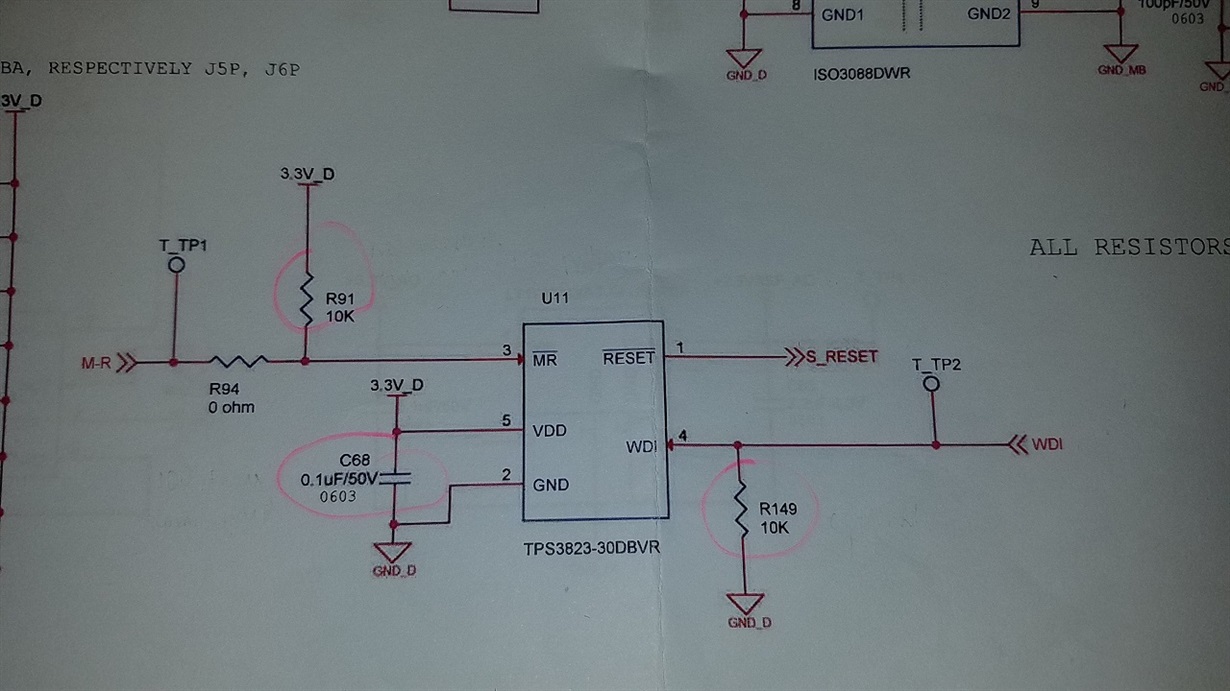

I am seeing an issue with the RESET output of the TPS3823. The RESET output stays LOW after I give it a 1ms low pulse on the MR pin. I am supplying a 400ms periodic pulse on WDI pin. And I have verified that I am getting a RESET pulse output when I disable the WDI pulse. What else am I missing?

Thanks,

Jeffrey