Other Parts Discussed in Thread: TIDA-00778

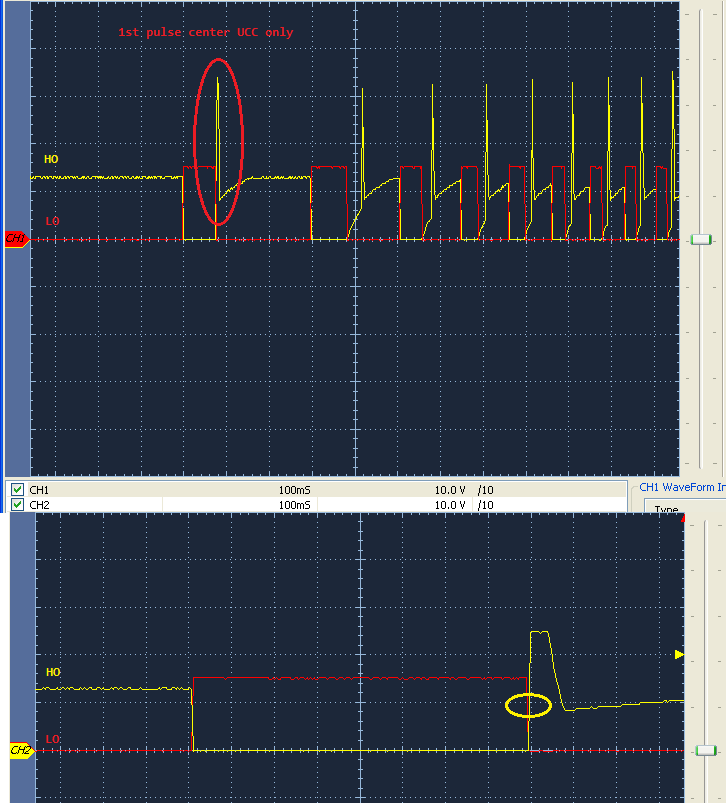

Three phase motor 12.5kHz PWM commutation 100VDC cause random failure to HS/HO junction, no signs of under/over shoot HO via soft turn on/off compensation resistors.

The means of using soft or even hard NFET turn on eventually damages HO Totem pole, stresses HS/HO internal NFET. Such results in leaking VDD supply onto 1/2 bridge inductor raising typical 12.6v floating bias to nearly 14.3v, e.g. HB leakage via HS/HO breakdown.

Conditions: 80us overlapping PWM drive signals HI/LI inputs, LO/HO:130 ohm GTon, 24 ohm GToff (parallel R/Schottky), NFET Qg=<96NC @VBpin=13.6v

Contrast: Other vendor 600v gate driver (IGPK +/-600/350ma PW<10us) never fail similar described leakage, mandates unwarranted chip replacements.

1. How can maintaining IGPK +/-4amp (PW<10us) ever cause HO/HS stress via 130 ohm GTon 24 ohm GToff resistor?

2. What is work around to stop HS to HO reverse leakage path from developing in first place, typical HS pin R value?

3. Why does HO/HS leakage path failure cause uncontrolled and very high inductive voltage overshooting?

4. Zener diode (15.2VzMin, 16.4VzMax @10ma) or 10k protection resistor placed across HS/HO, regulates floating VB the cause?

5. Any Wiki report updates how to correct HO side gate drive failures caused from industry typical configurations?