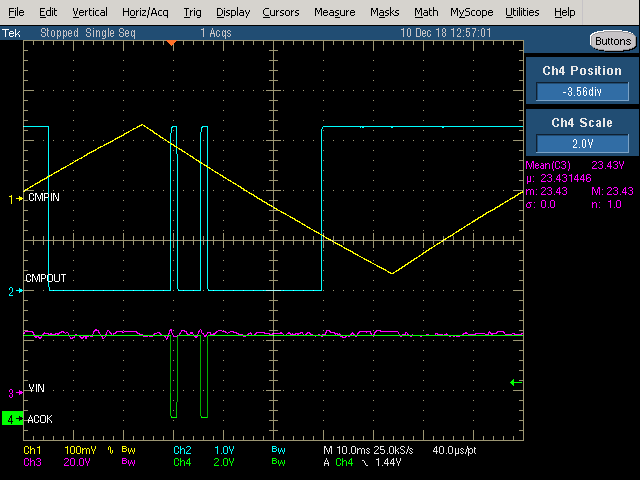

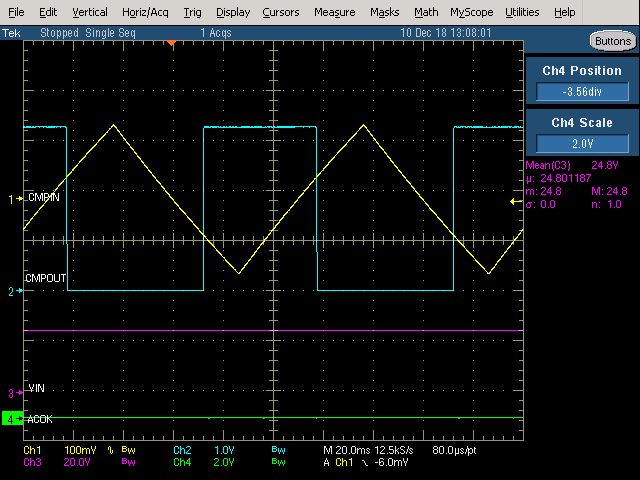

I catched a waveform just shown below. The yellow channel is CMPIN, and the blue channel is CMPOUT.

When the CMPIN is higher than 2.4V, CMPOUT will reduced to 0 last only 28ms, then CMPOUT will rising again.

When this happened, the IC may be influenced by the OVP, which is because I pulled the input voltage to 30V.

So, why the CMPOUT rising again, dose this have anything to do with OVP ?