Hi,

At Fault delay function I have some question.

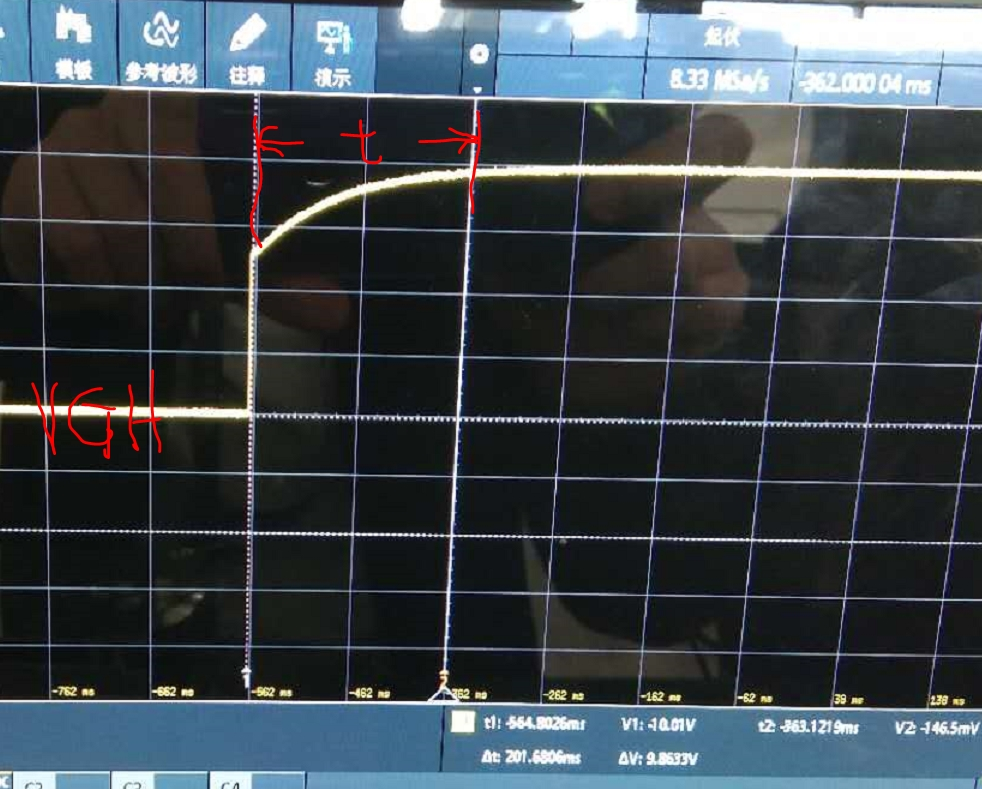

As below pic, it's VGH startup time about 200mS.

Does it mean that if one or more voltage rise times of AVDD, VGL and VGH exceed the delay time of fdly capacitor settings,

there is only a probability that the chip latch will occur instead of 100%?

Why is it not 100% latch status?

thanks.