Hello,

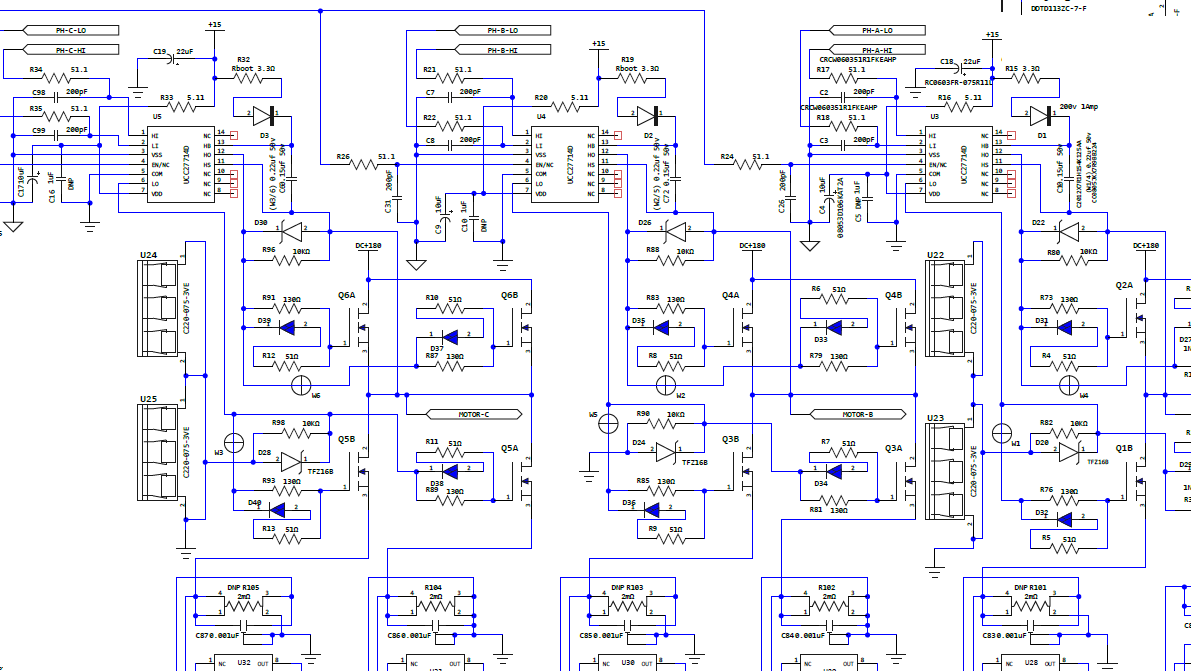

After install new UCC we check diode drops are consistent pin to pin against other mounted UCC. Oddly a few new devices produce 1.94v drop HO-HS and >503mV (HS-HO). The 1.94v drop occur only center gate driver 16v zener read both ways parallel with 10kR placed across HS-HO pins. Remove zener tests ok replace it with new one still have 1.94v drop one way 503mV drop reversing probes. Same after replace HO NFET for good measure after two UCC have failed HO-HS, bad read 1.34v drop same direction 1.94v drop of working UCC only on center gate driver. Oddly 1.94v drop is not typical on any UCC out of circuit HS-HO drops in one direction only. Yet some known bad UCC drop both ways 1.34v swapping probes on pins, out of circuit. Don't recall ever having zener (HS/HO) 1.94 drop center UCC, typical 0.7v drop one way only. Have checked PCB for solder splash ball shorts, none are present though three phase commutation succeeds well for some time before shorting of HS/HO occur.

How can only center UCC HS/HO have voltage drop in both directions when other two UCC do not, three identical circuits no inductive loads attached?

Is it possible there are some production issues with this device that got past QC?