Other Parts Discussed in Thread: BQ40Z50

Hi There,

I have been having issues recently with discharge FETs failing in my battery packs, leading to free discharge of the pack. This causes many protection issues, especially the lack of under-voltage and over-current protection.

A schematic snippet of my design is as follows:

This design more or less follows the reference design with added TVS gate protection on all of the FETs

The FET I selected - for its low resistance - and in line with the design recommendations is this (data sheet):

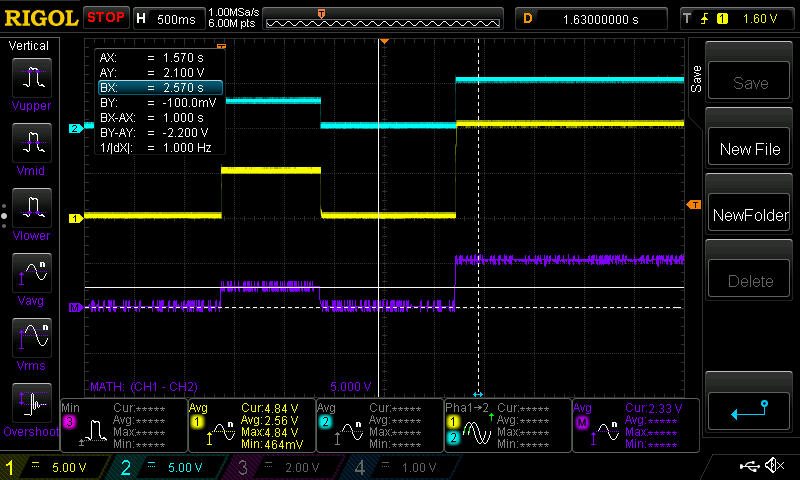

The death of the discharge FETs seems to be happening under usual operation conditions (not strenuous tests) and is only realized when the pack fully discharges and it fails to turn off (despite the gas gauge attempting to - as verified by scoping the DSG net). This issue seems to be limited to the discharge FET as I have not observed any issues with the others.

In addition to the protection shown in the schematic above the pack as a whole is protected with spark gaps and the following TVS diode.

http://www.vishay.com/docs/87649/tpc11cathrutpc36ca.pdf

Does anyone have any insight as to what might be causing these issues / what I may have overlooked?

Thanks,

David