Part Number: TPS40170

Other Parts Discussed in Thread: LM5146-Q1

Hello everybody,

Our product using TPS40170 failed on EMC radiated test at ~96MHz - so it's definitely common-mode noise problem! We narrowed it down with EMC probes and Spectrum Analyzer and we think the problem lies in buck.

My schematic is:

During PCB layout I paid attention for "power" loop to keep it small as possible. Layout looks like:

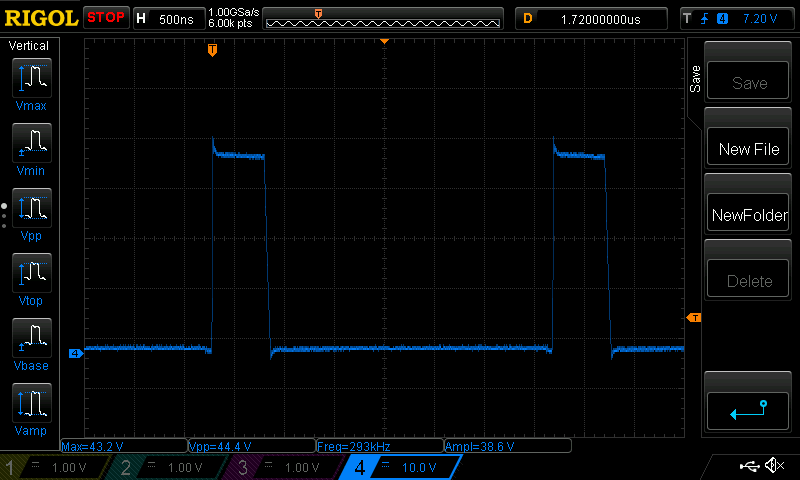

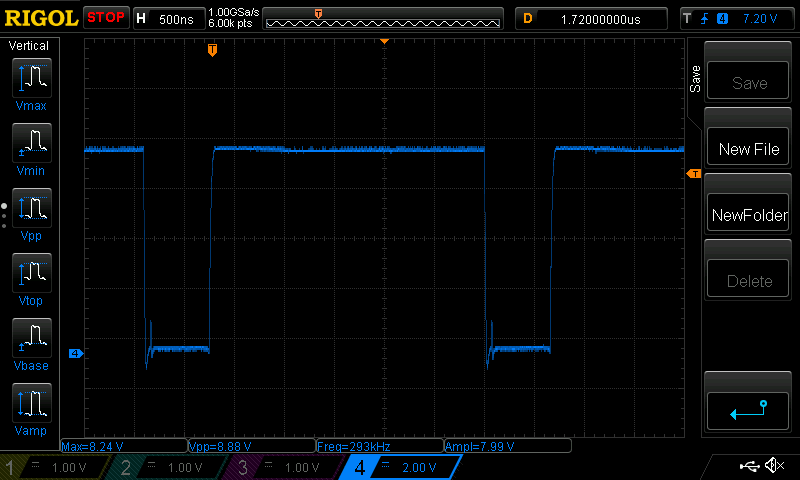

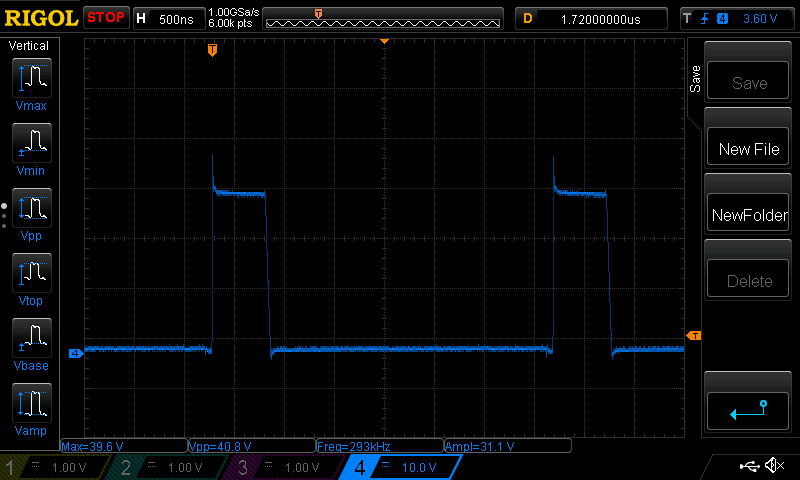

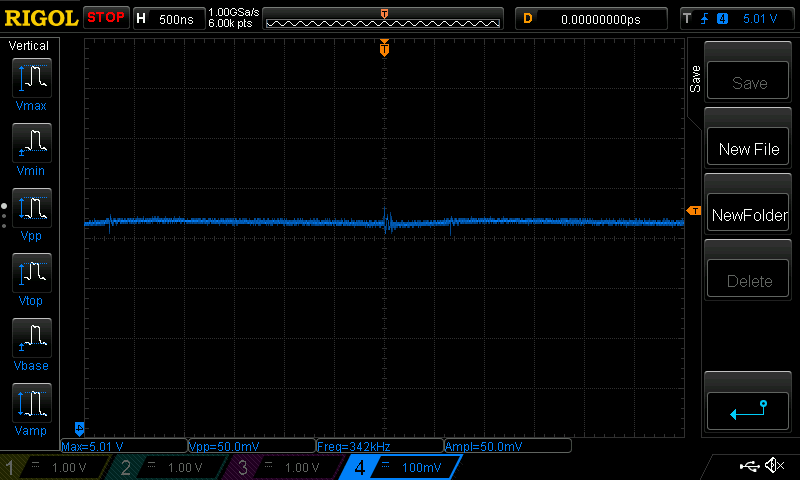

I did measurements on some critical points of the system: SW, LDRV, HDRV, OUTPUT node using "short ground probe".

HDRV node:

LDRV node:

SW node:

Output 5V:

Of course, one of the possible solution is to add common-mode clamp on the input, but I would like to mitigate the source as much as I can.