Other Parts Discussed in Thread: AMC1301, TIDA-01541

I am designing a power supply for a variable frequency drive by following the design of TIDU412A. The power supply gets input DC voltage from the main vfd rectifier; I have excluded the diode rectifier at the input of the power supply and my power supply design starts from L1 and L2 inductors of schematic 8.1 and follows the rest of the design as detailed in TIDU412A.

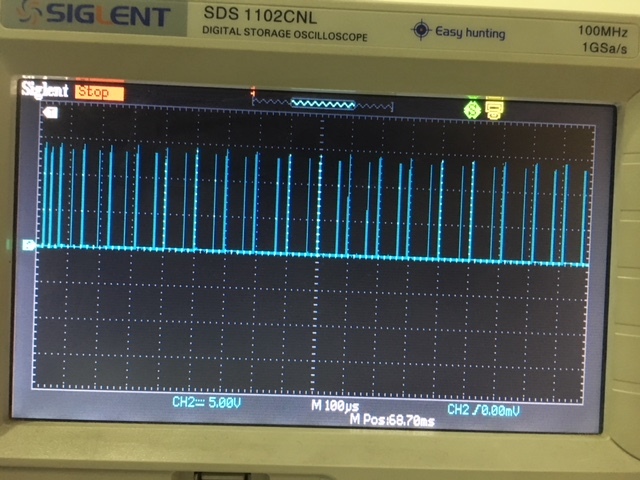

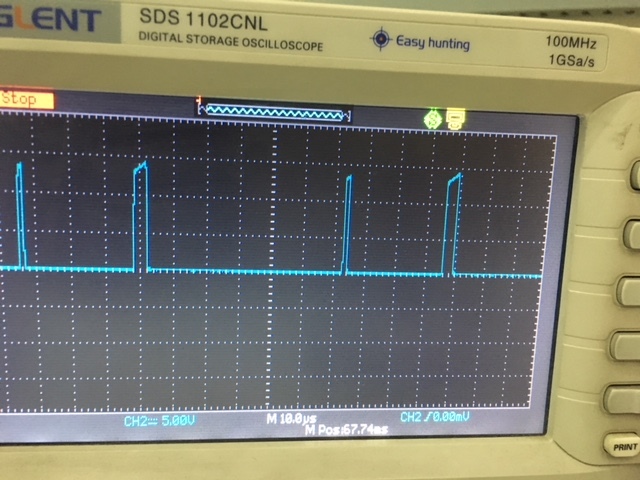

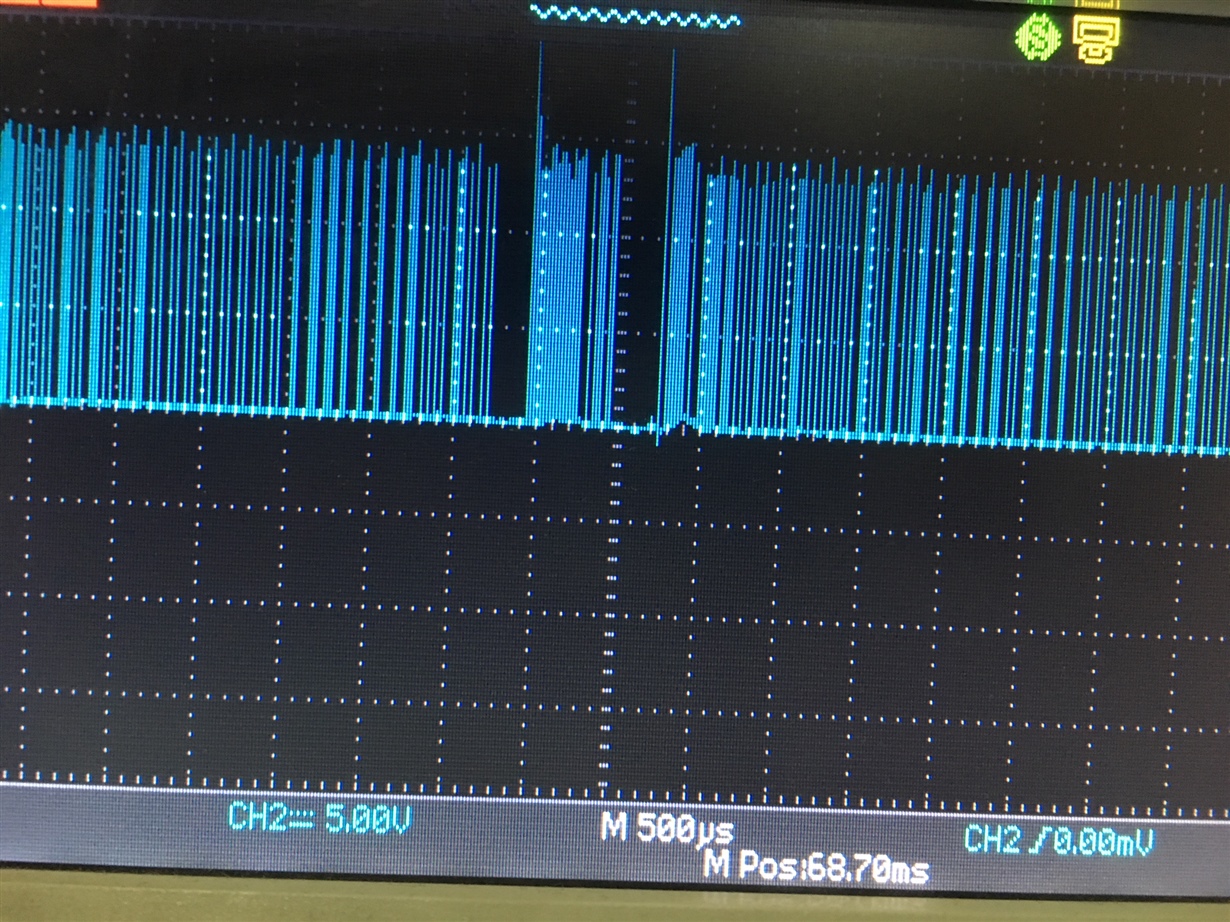

I am checking the voltage at connector j=J5 coming from vdc_meas in 8.1.It should reflect the input dc voltage(divided by turns ratio and through the resistive divider) but this result is not consistent when I change the input dc voltage.

Kindly help me out with this.

The schematics(PAGE 31) and design are with reference to TIDU412A:-