Hi Guys,

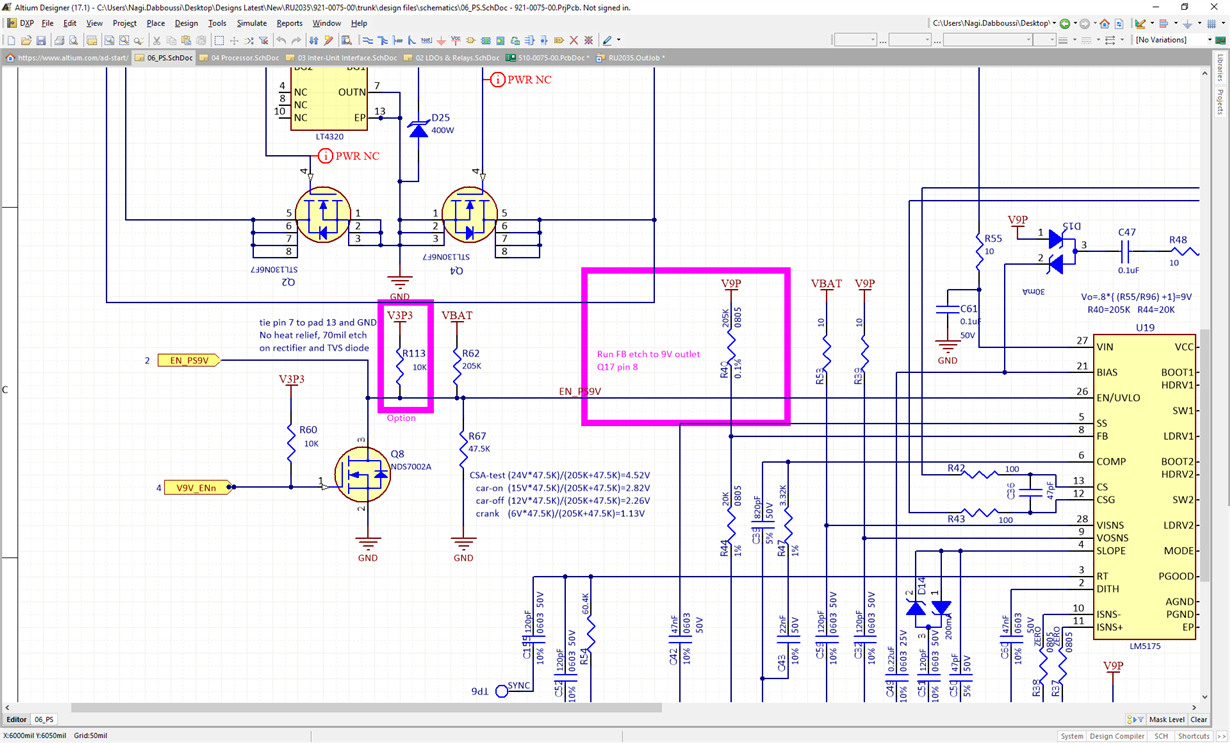

My customer is changing the EN/UVLO settings away from from 3.3V (10K) pullup to

VBAT and a divider of 205K and 47.5K.

Do you see any issues/concerns with these values?

math is on the sheet below.

Really concerned with the value for crank (below).

Does this fall into line or do I need a higher value?

Thanks,

Brian