Other Parts Discussed in Thread: TPS565208

Hello Community,

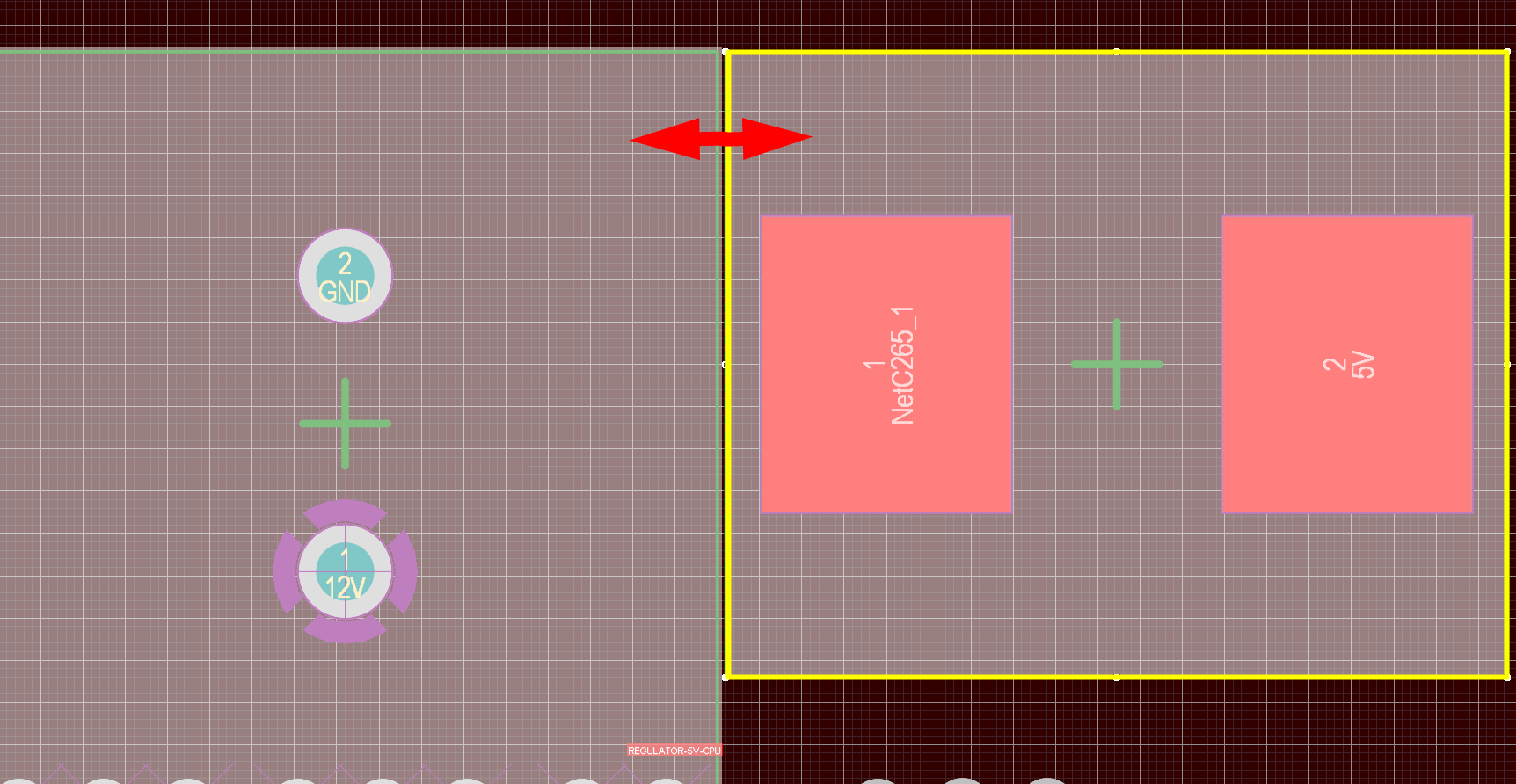

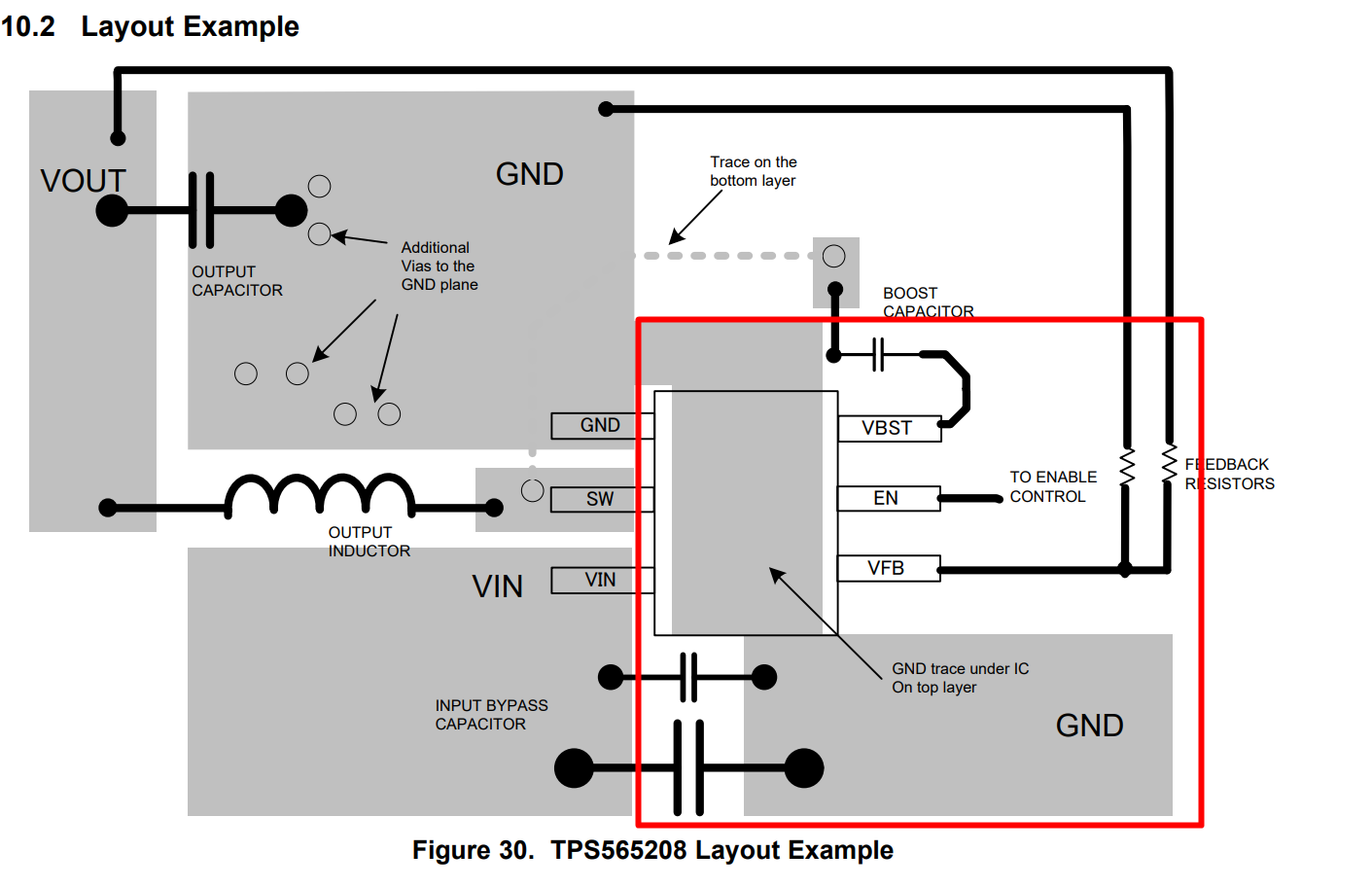

1. Tell me, is it necessary to isolate (cut copper) the area (placement area) located directly under the inductance from any passing signals, for example, from passing GND? (yellow border)

2. Is it necessary to indent elements of topology (capacitors, etc.) from the inductor if it is fully shielded? If so, what should be its value? (red arrow)

Description:

Left - Capacitor (VIN), Right - Inductor (VOUT)