Hi TI experts,

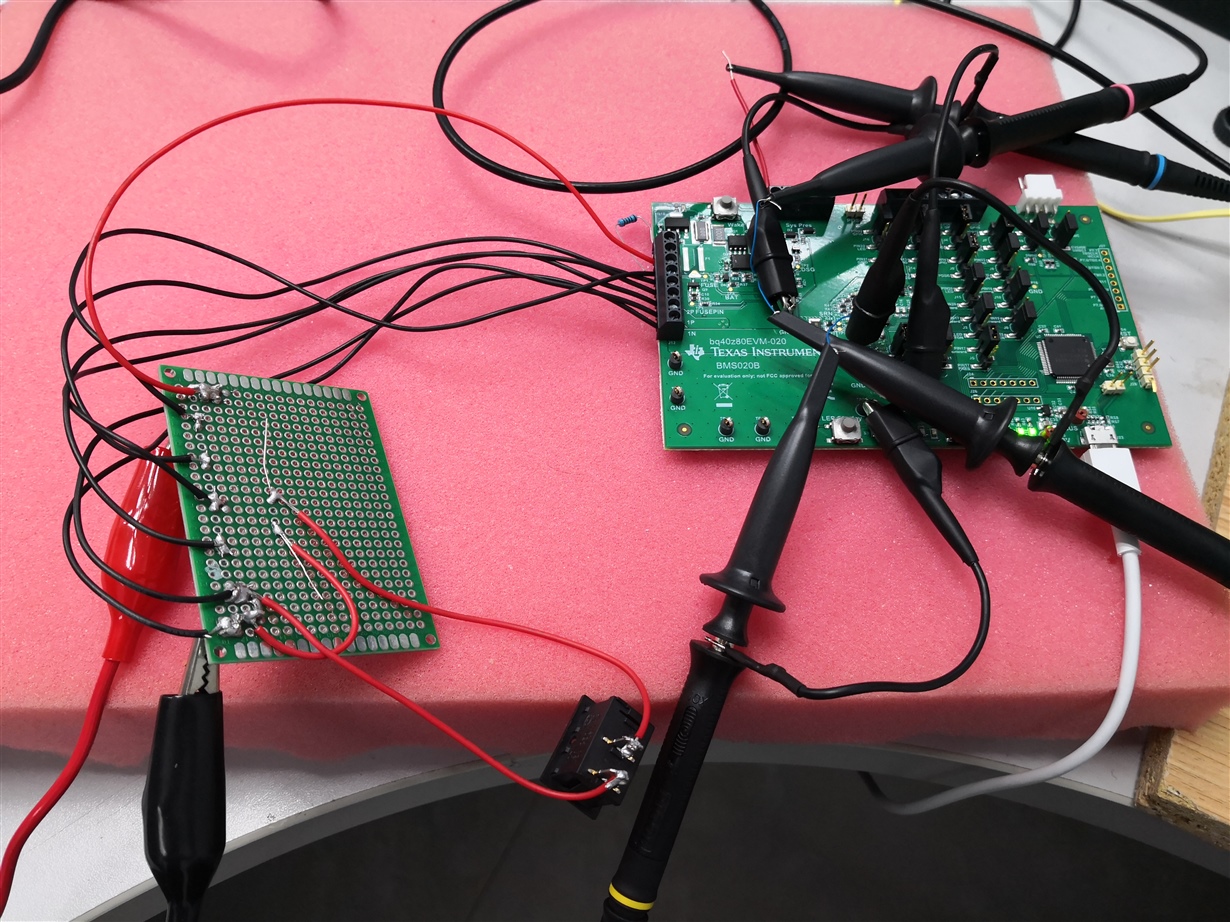

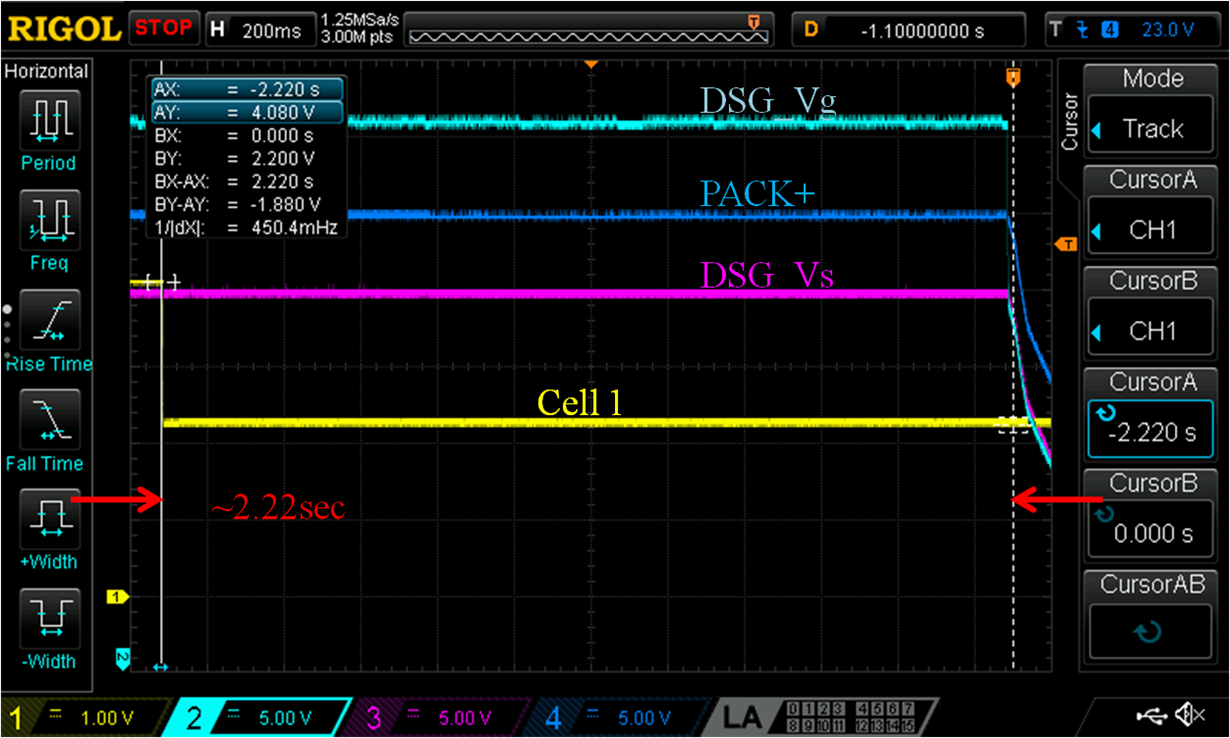

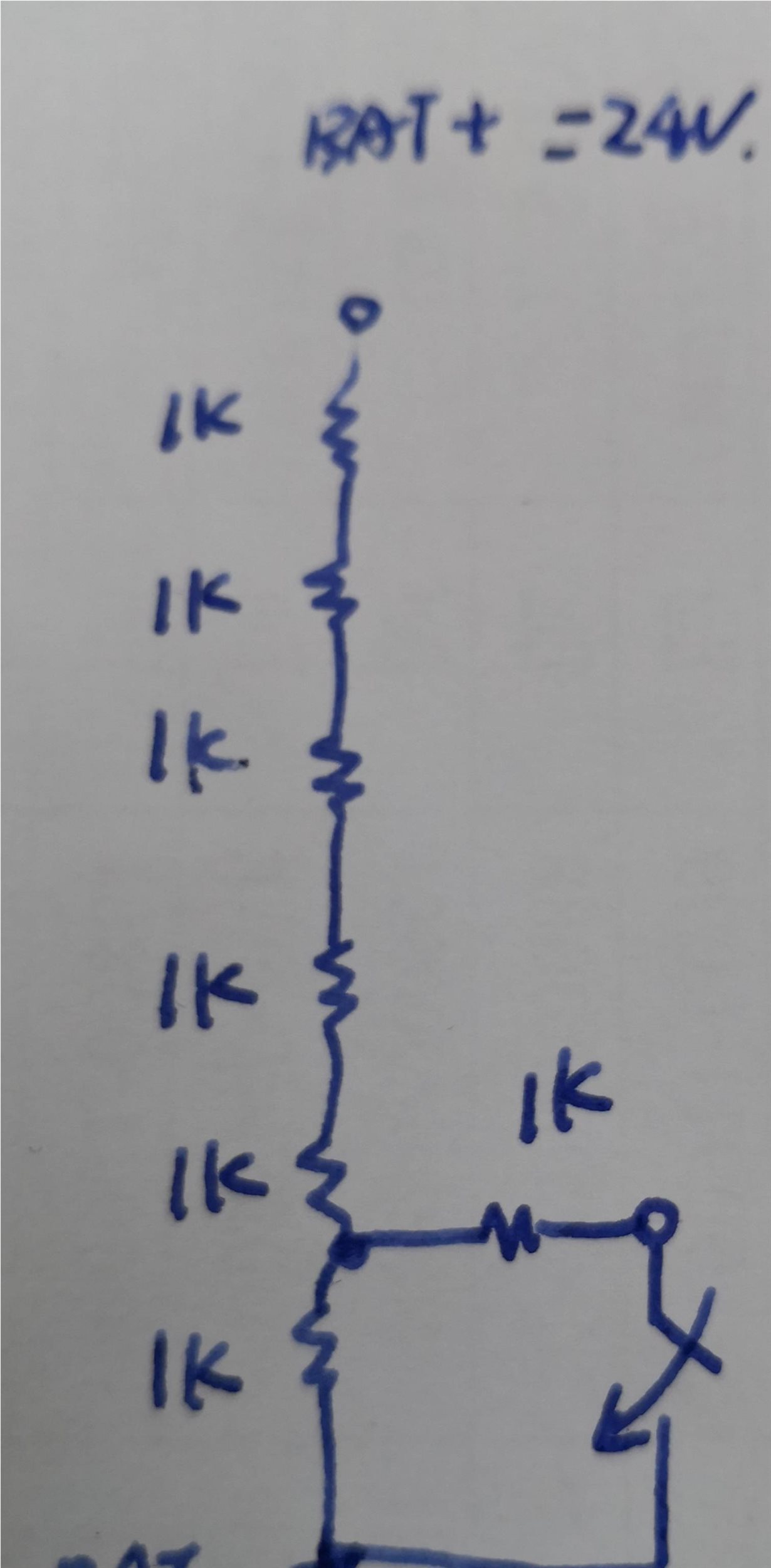

I set EVM board CUV delay is 1sec, but the test result is 2.2 sec. Why is so longer than my setting? I used DC=24V and six 1k ohm resistor to simulate battery, and parallel a switch at cell1 which series a 1k ohm for CUV test. CUV will happen when I turn on the switch. Below waveform is test result, CH1=Cell1, CH2=DSG mosfet Gate voltage, CH3=DSG mosfet Source voltage, CH4=Pack+. Pack+ without load and without SMBus communicate. I find TRM has a chapter "Sample Filter Settings", is it relate CUV delay longer than setting?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.