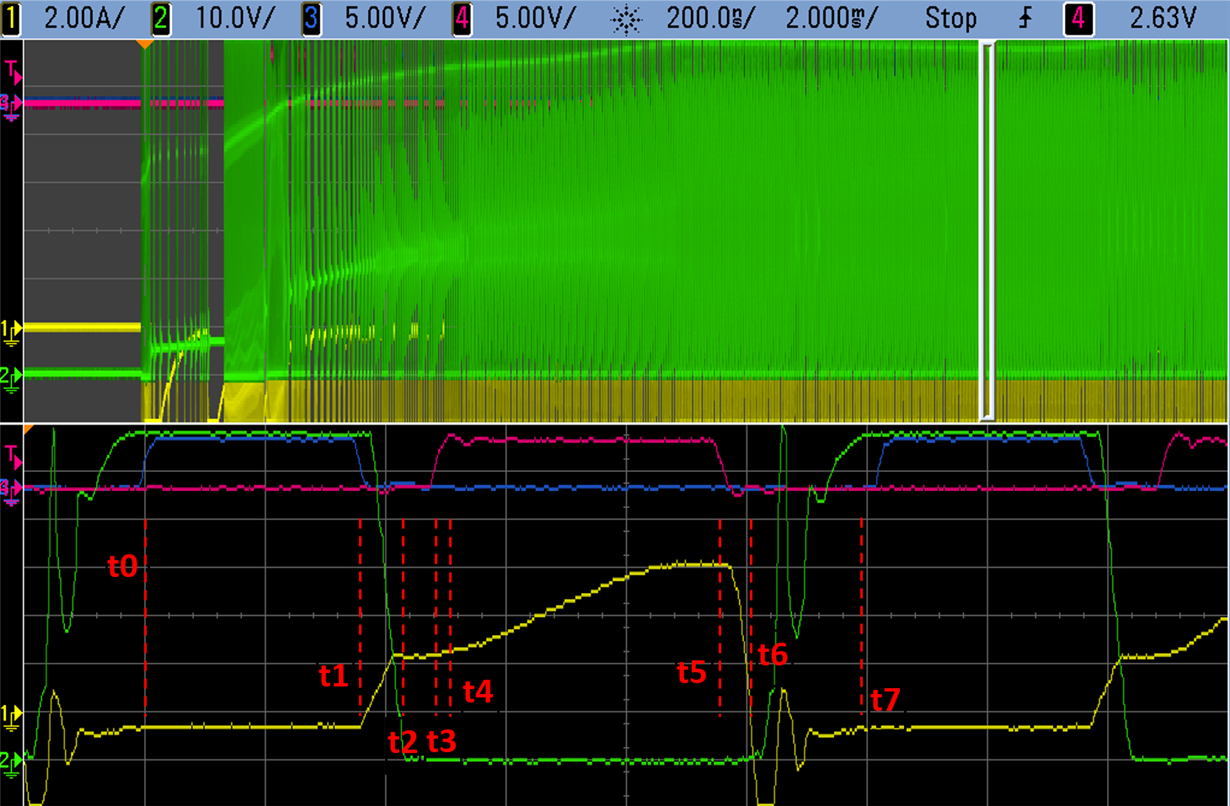

I have my supply going, but timing and resonance seem to be off or drifting. In ABM burst mode I typically see a couple good switching cycles and then I start to see the switch node voltage not dropping to zero after PWMH goes low. This causes the next PWML to be late and to miss zero-voltage switching. I am operating with SET = 1 which is normally used for Si FET switches, but my high-voltage GaN switches have large output capacitance so SET = 0 switches too quickly.

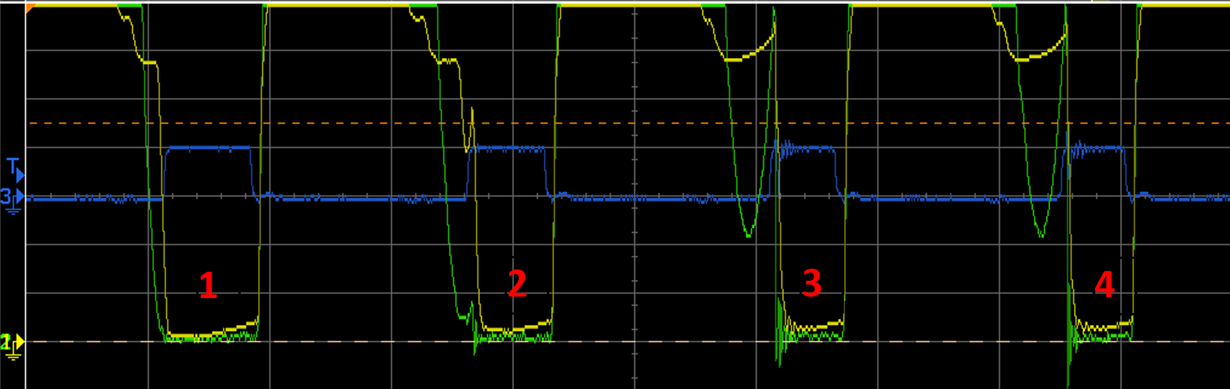

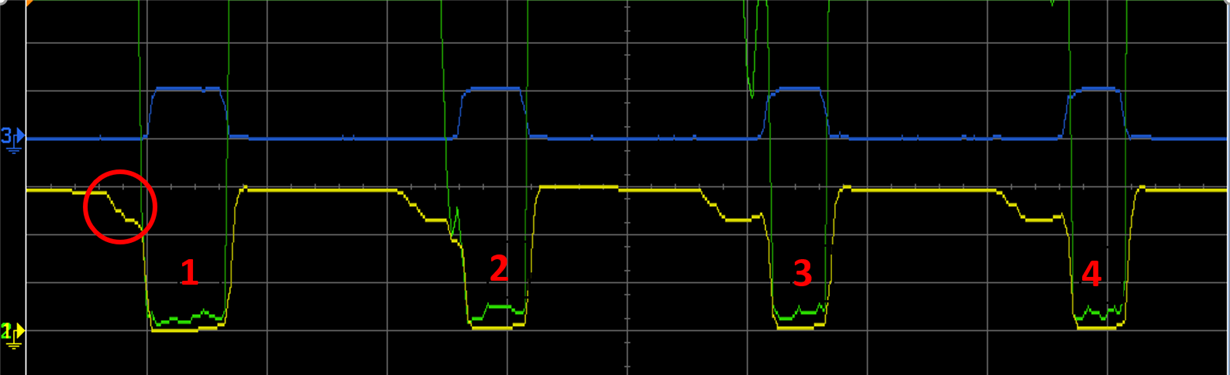

The traces below are yellow = SWS controller input at 2 V/div, green = high voltage switch node, captured at 100 V/div and zoomed in to 20 V/div with high-res capture, and blue = PWML at 5V/div. Cycle 1 is normal, 2 is marginal, and 3 and 4 show the switch node voltage not reaching zero and late PWMLs. The upper dotted line cursor is 9V, the SWT threshold to generate a PWML pulse. You can see that SWT doesn't reach this threshold in pulses 3 and 4.

This behavior doesn't change with line or load, and I have tried a range of clamp capacitor values about 5:1. I should also mention that my secondary current waveform doesn't look right either. Instead of starting at zero after PWMH goes high it jumps to 2 - 3 A and seems to be resonating at the wrong frequency. That sure seems like a bad clamp cap value, but changing that has little effect.

Any ideas?