Hi

For my first question on this forum, I'd like to describe the following case:

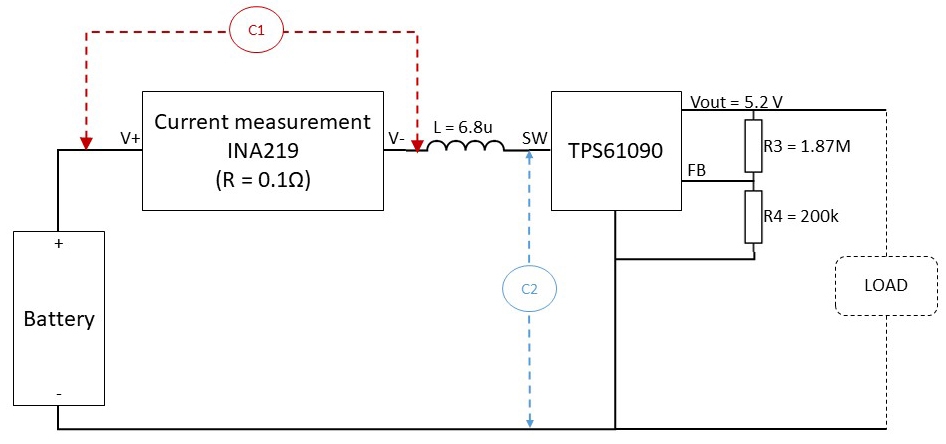

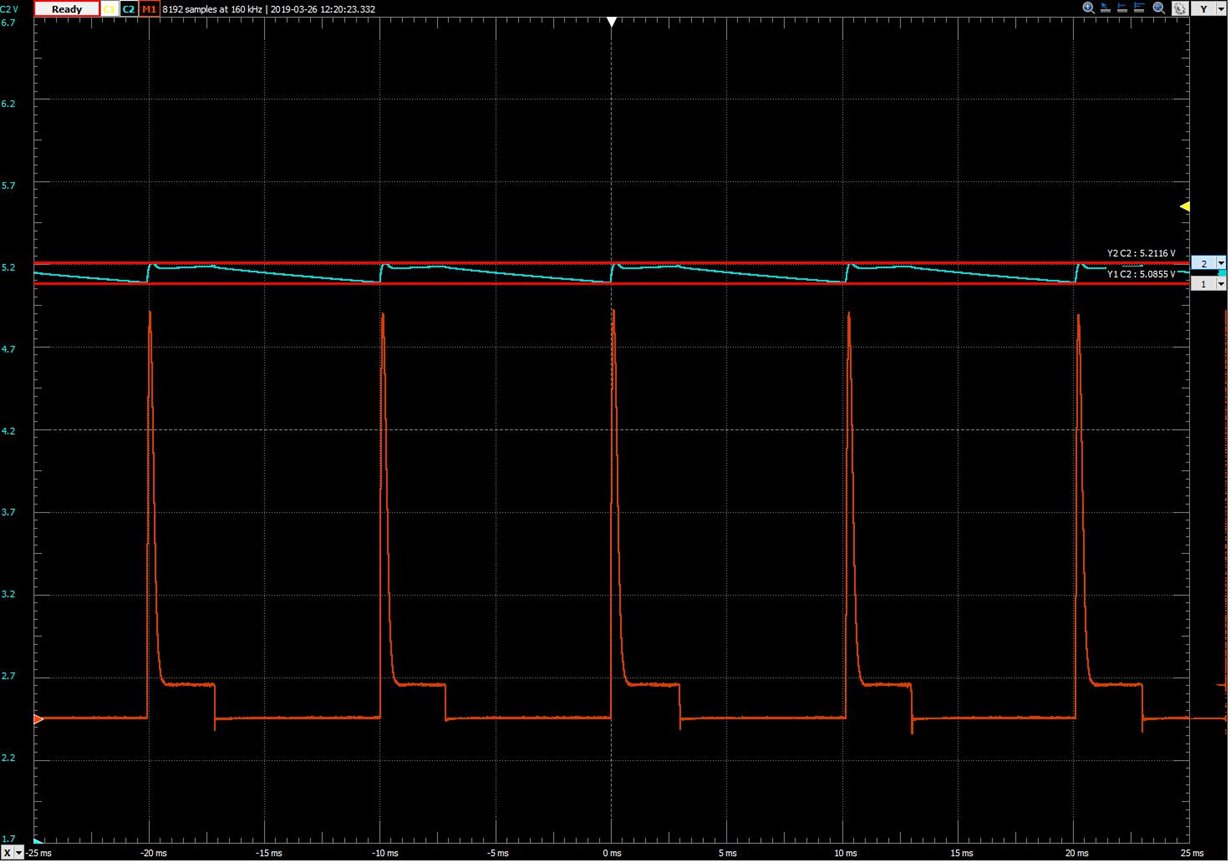

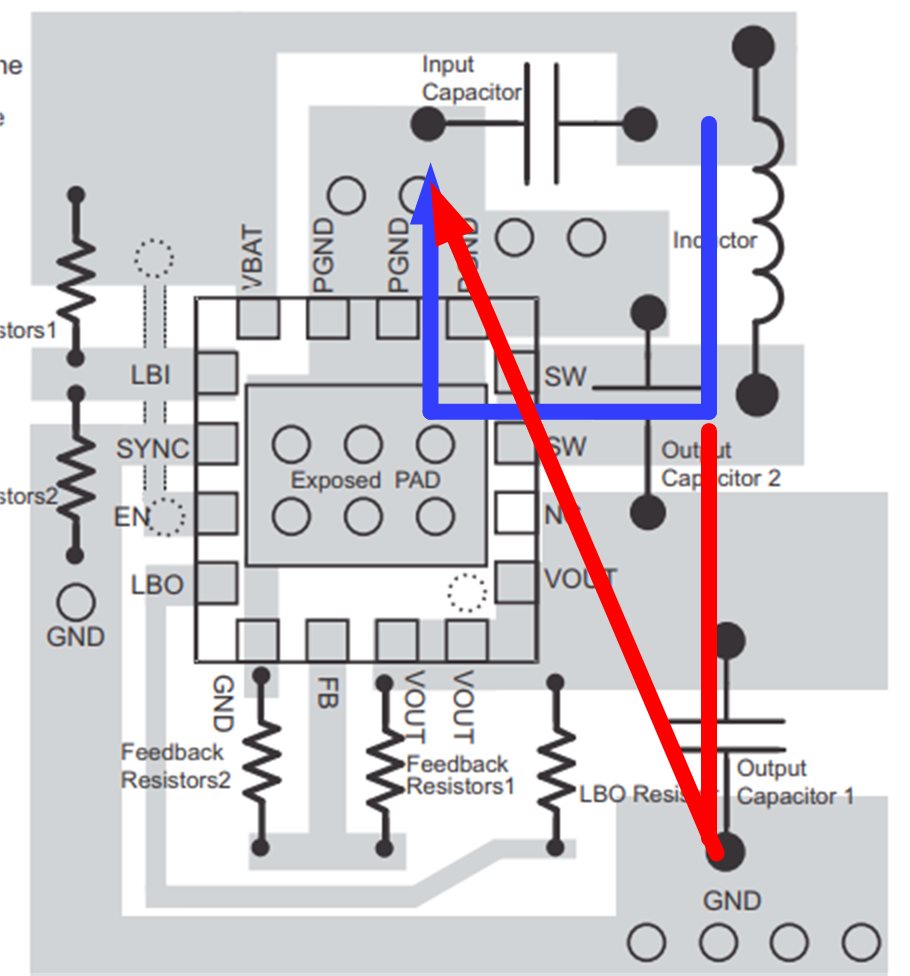

- I have a TPS61090 with single cell battery input which provides 5.2 V to a microcontroller (NXP Kinetis K66) and an analog audio amplifier circuit (after a double LC filter, not on the schematic capture). In working mode, the circuit seems to work well and the SW pins switch at 600 kHz as they should.

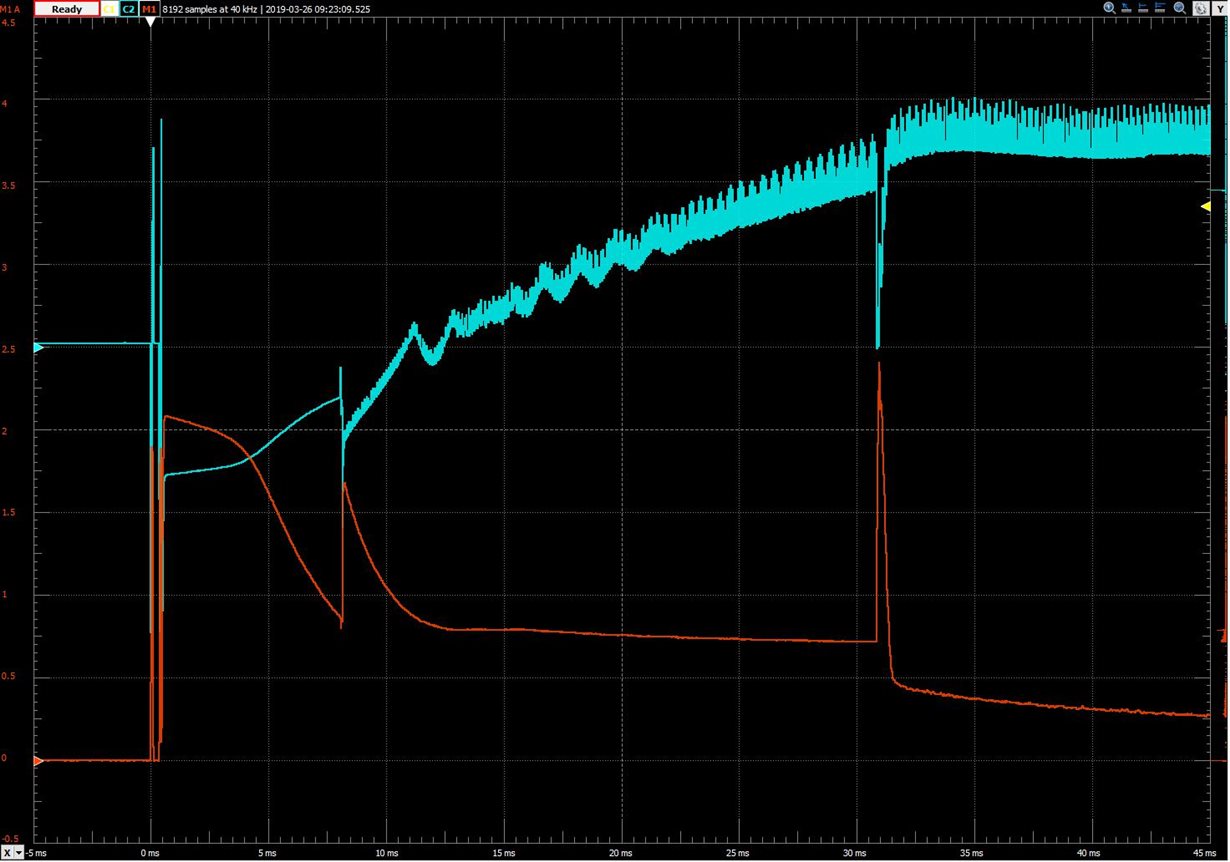

- When the microcontroller is set to low-power mode (VLLSx), the SW pins alternate switching/stopping at about 100 Hz. And when the switching sequence starts, one notices an important voltage drop (up to 500 mV) in the battery, which corresponds to a ~1.5 A current peak... not really what I am looking for at low-power.

Do someone have an idea, why the behaviour changes with the power mode? Can that du to the 4700 uF capacitor (C8) that I put at Vout to smooth the output?

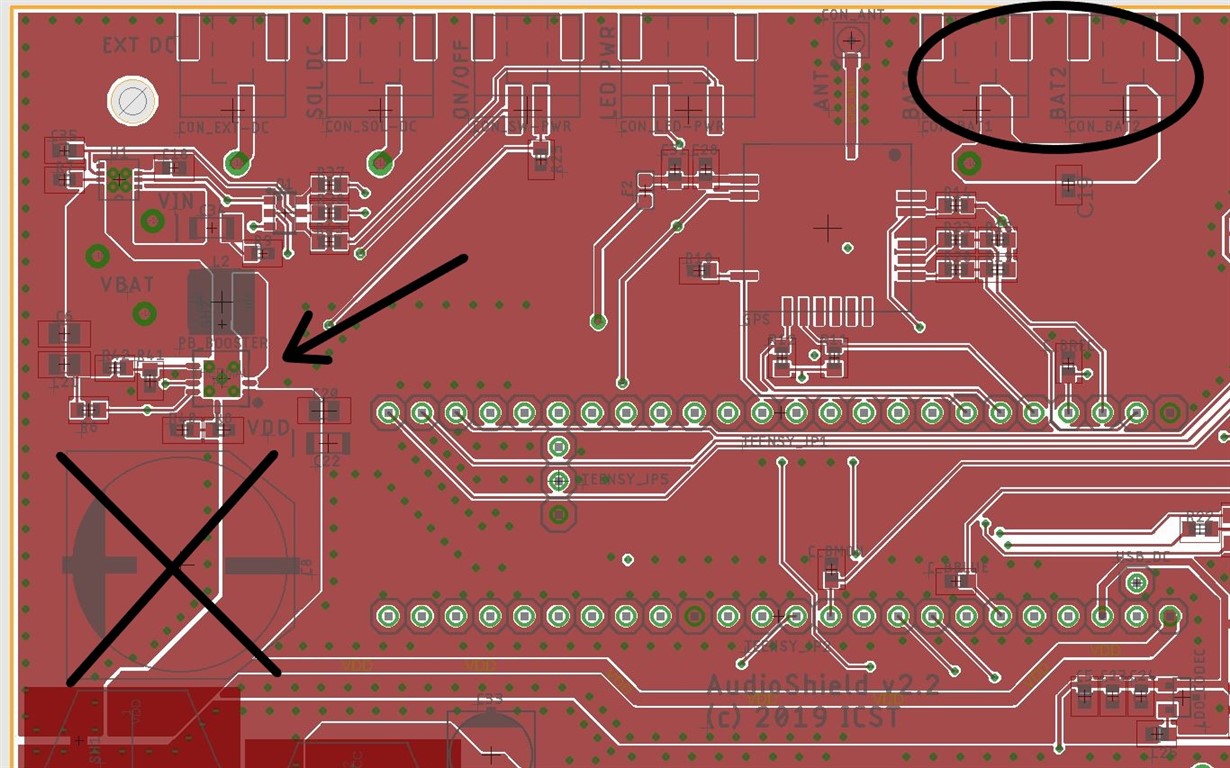

I can provide some layout documents and oscilloscope captures when I'm back to the office. But my mistake is perhaps so big, that someone can tell me straight away what to change...

Thanks in advance for any advice.

Best, Sébastien