Other Parts Discussed in Thread: AM3358,

Hi,

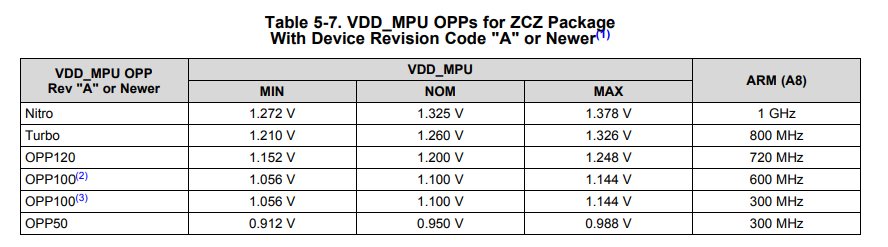

My customer is evaluating the TPS65218D0 and AM3358.

PGOOD failure occurs on DCDC2 when output voltage drops by DVS at light load as attached.

When output capacitor is below 50uF, this failure does not occur.

So, I think that the cause of this failure is slow discharge from DCDC2 output.

1. Is there any workaround for this failure?

Though they have already confirmed to improve by STRICT = 0b setting, this can not be applied by restriction of AM3358 side.

2. Though DCDC2 output capacitor is recommended ~500uF on the datasheet, is this considered to use DVS function?

Best Regards,

KuramochiTPS65218D0 PGOOD Fail.xls