Other Parts Discussed in Thread: TINA-TI,

Tool/software: TINA-TI or Spice Models

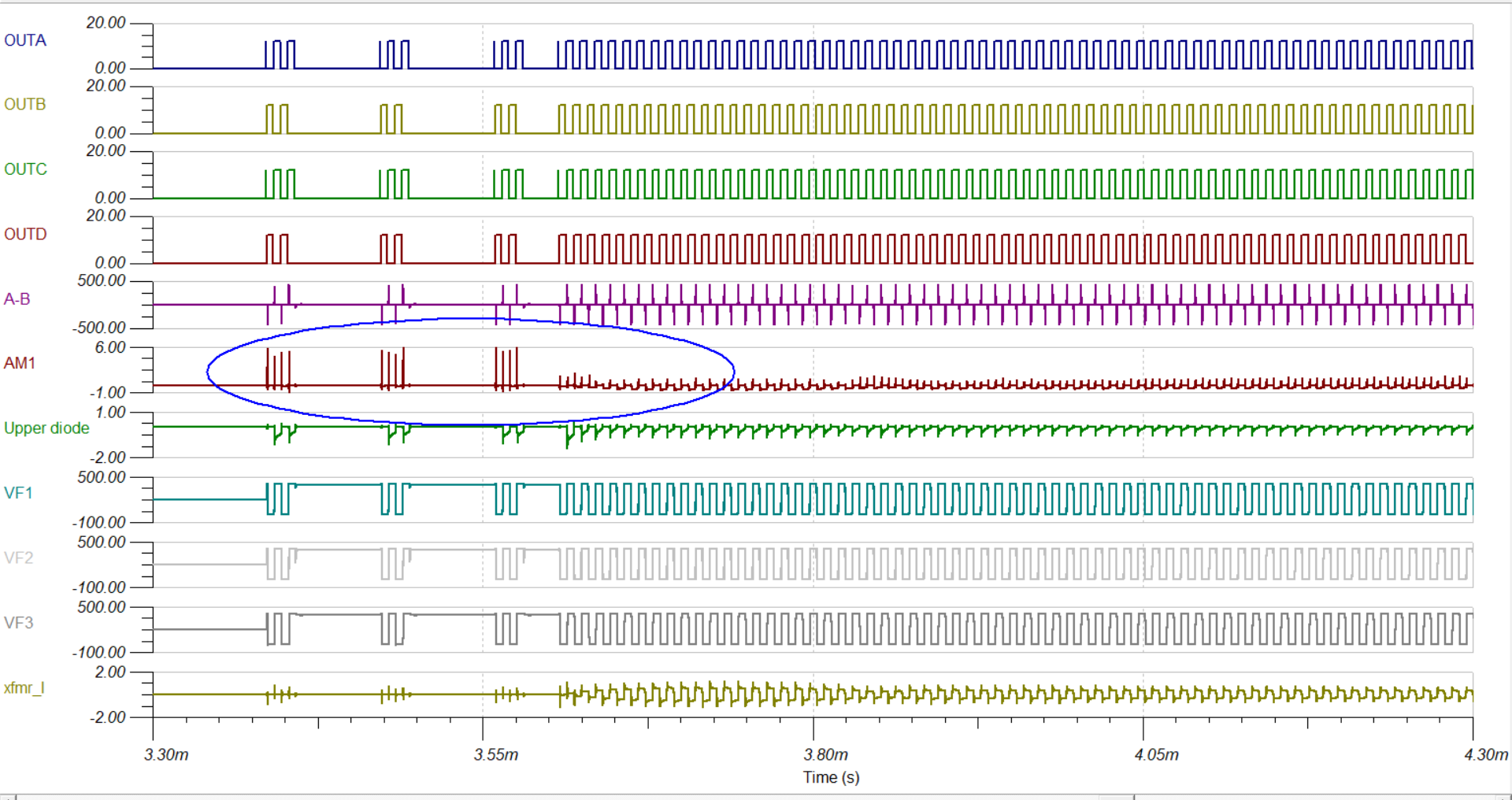

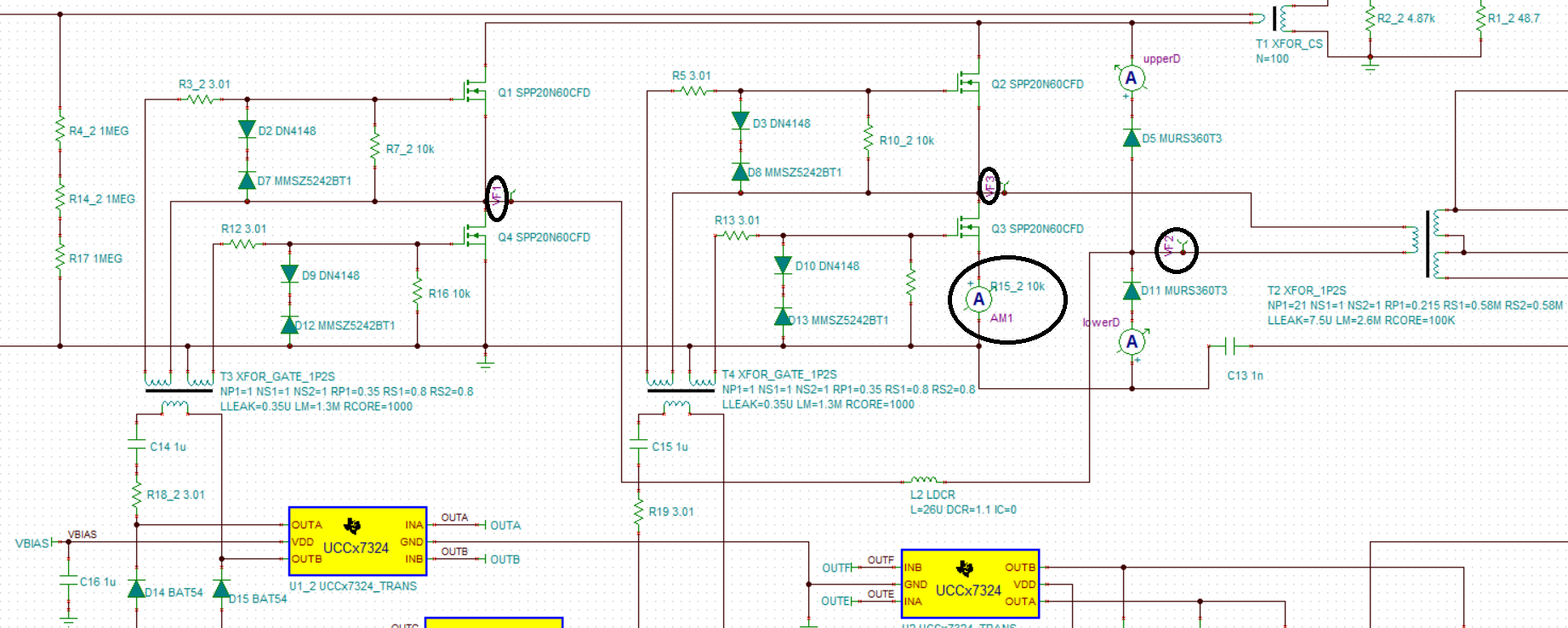

Q1. In which mode (burst, DCM or CCM) controller working at startup of UCC28951? because initially from 3.40m to 3.65m waveform looks abnormal in TINA TI Transient start up simulation of UCC28951. AM1 is current through Mosfet Q3, why it is much higher initially as highlighted and then reduces afterward.

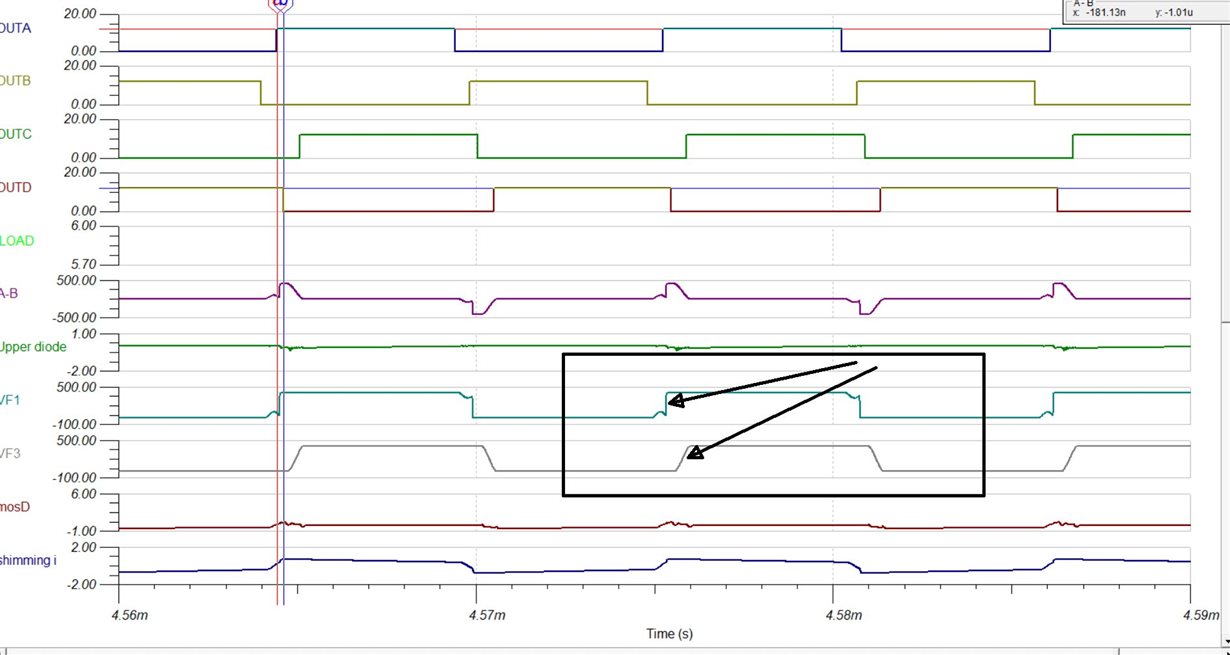

Q2.Why in simulation during startup voltage at VF1 i.e at source of Q1 and at VF3 source of Q2 Voltage is high when there is no gate pulses. (attached schematic)