Other Parts Discussed in Thread: UCD3138, UCC27211

Hi,

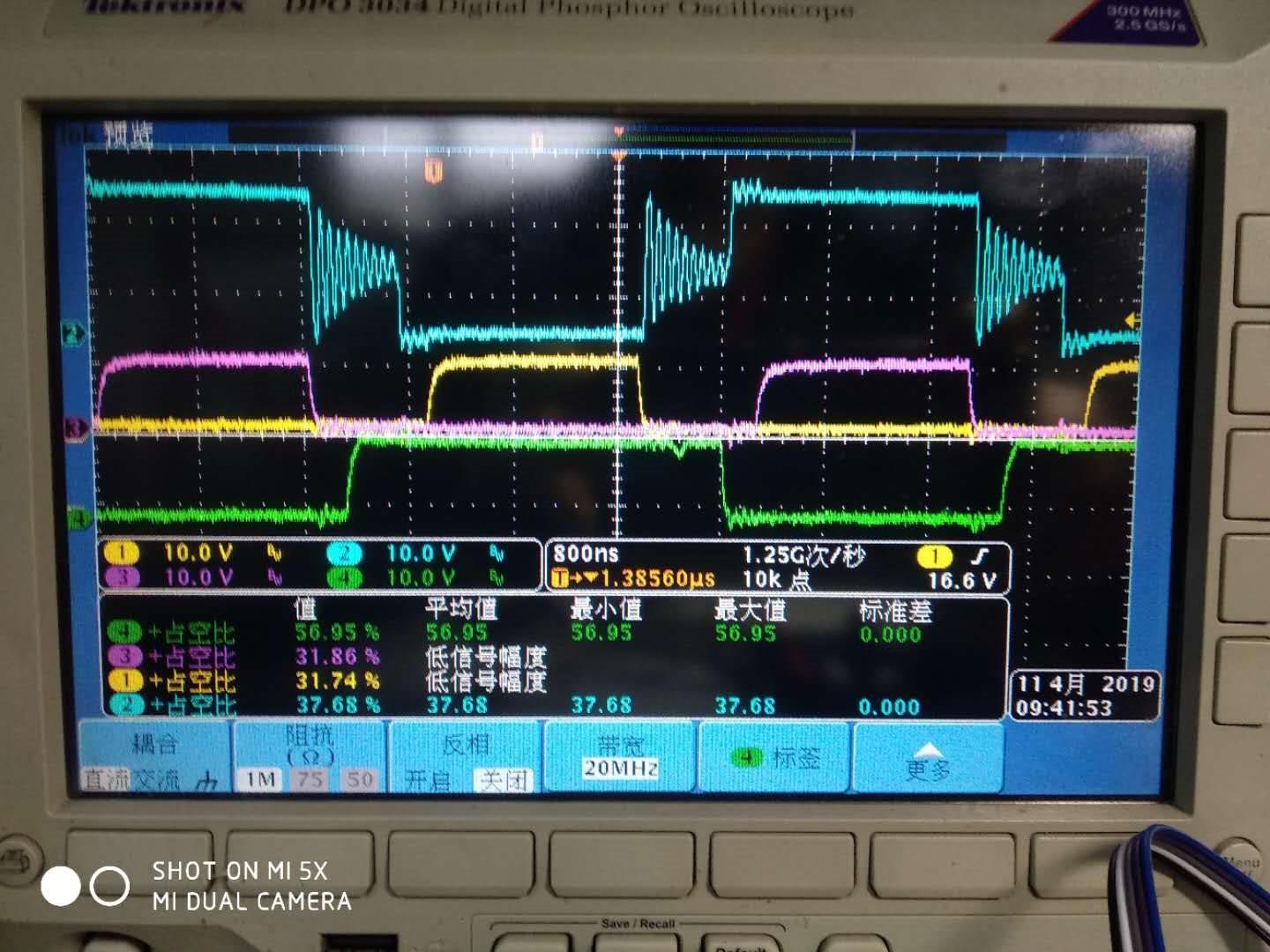

I made a full bridge circuit modeled on the UCD3138's full-bridge hard-switch development board.

Since the primary MOS transistor driver I used was not UCC27211, causing the PWM signal to be delayed by 200ns, I tested the delay of the UCC27211 by about 30ns, and the circuit PWM drive timing changed.

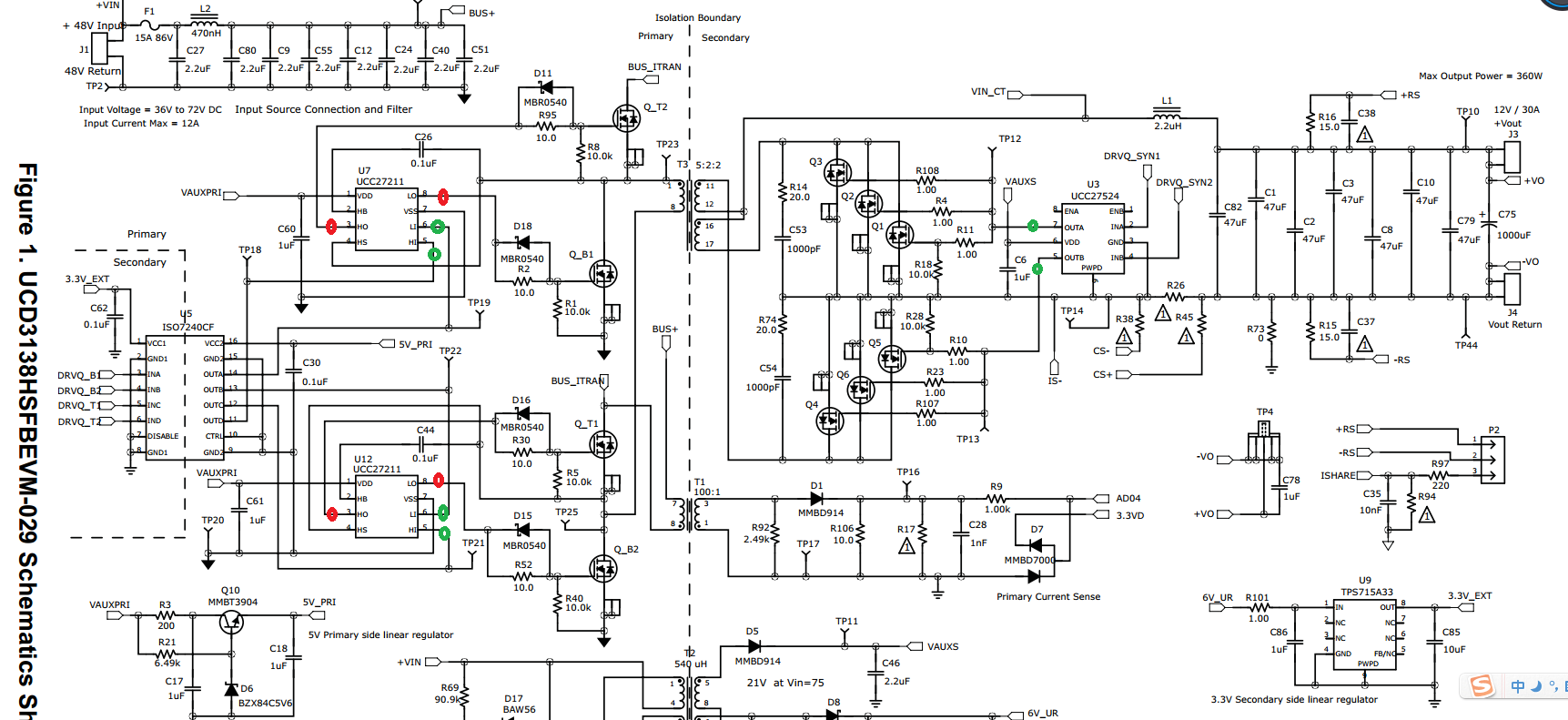

The primary MOS transistor and the secondary synchronous rectifier are driven as shown above. Purple and green are primary drivers, and yellow and blue are secondary drivers. It can be seen that a 200 ns delay occurs after the primary drive PWM signal passes through the driver IR2110. There is an overlap between the primary and secondary drive signals.

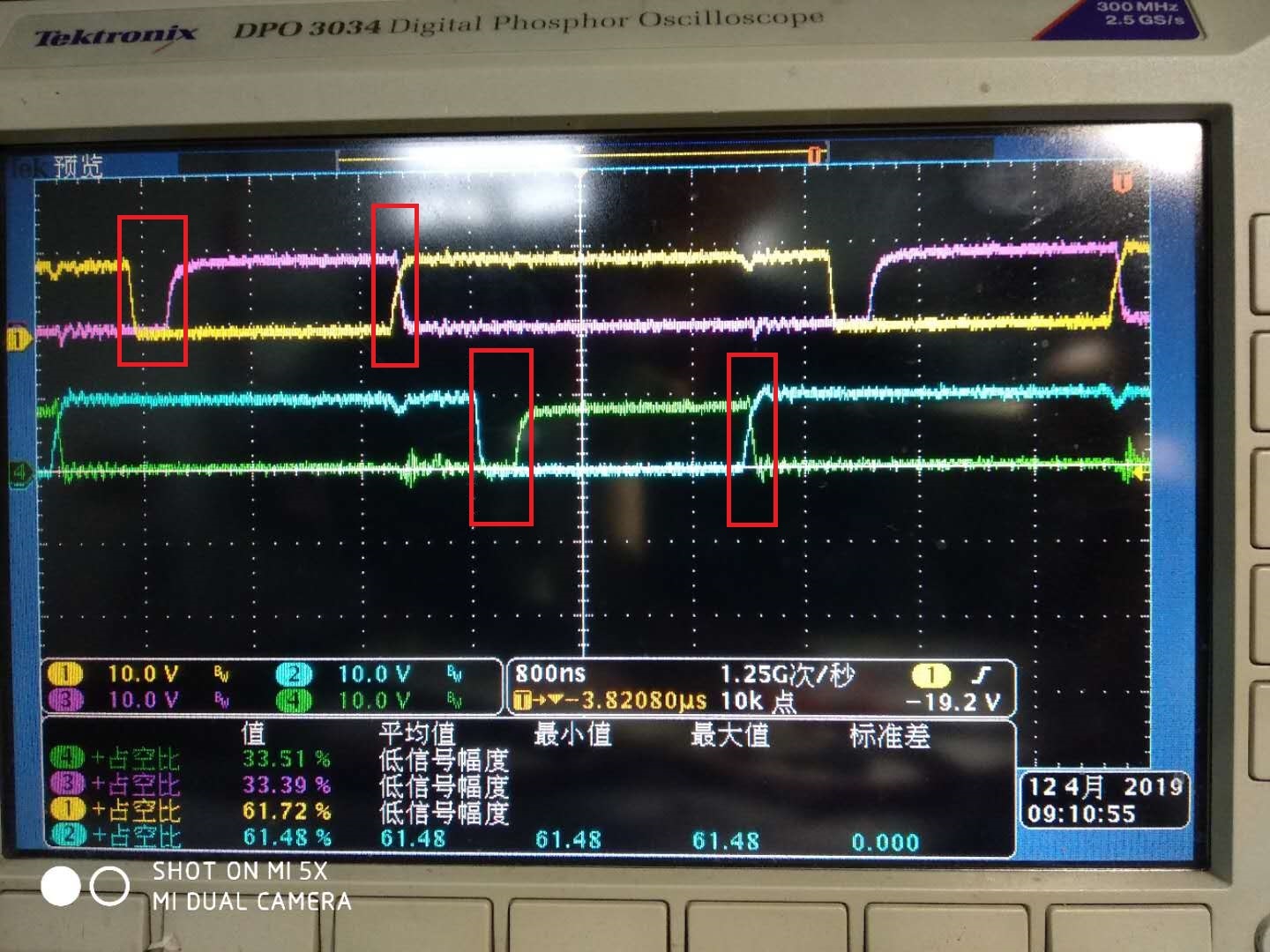

I tried to increase the dead zone between the primary drive and the secondary drive by 300 ns, so that the overlap area disappeared, that is, the on-time of the synchronous rectification drive signal was shortened. However, the circuit will oscillate again, as shown below:

I don't know why there is oscillation. At this point, the input current will increase by 0.6A. The phenomenon I observed was that by increasing the dead zones of the primary and secondary PWMs, although the overlap caused by the primary delay disappeared, the duty cycles of the primary and secondary drives also decreased. I can't figure out why the main circuit will oscillate? Or what method can eliminate the adverse effects of the 200ns delay caused by the drive IR2110?