Hi

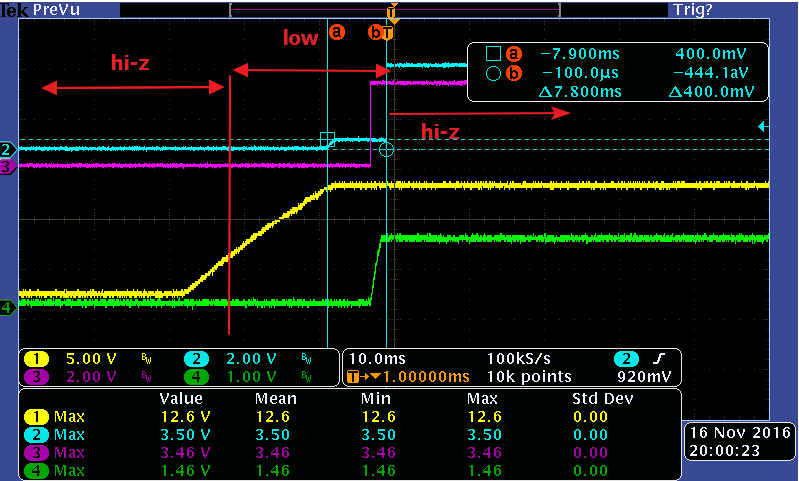

My design rest on the soft-start time and the delay of power-good. I see a strange discrepancy in the soft-start timing.

- I set 10nF as soft-start timing capacitor.

- Tss calculated from formula in datasheet is 1ms

- Measured Tss is about 2ms.

- Eval board use 8.2nF as soft-start timing capacitor.

- Charts from evaluation of example design in datasheet shows, that for SS capacitor Tss is about 2ms.

Please state correct formula for soft-start design.

State the accuracy of soft-start circuit over various conditions:

- Css charging current tolerance.

- PG delay accuracy.

- PG trigger thershold accuracy is stated already.

There is a second issue with the TPS562210A datasheet. The description of Power good delay timing is not as clear as should be.

- Please draw chart that explain timings.One picture will be more easy to interpret than 10 paragraphs.

Third issue: Charts of PG outputs in datasheet and EVM evaluation are wrong. The real behaviour is different. PG signal is held low, until some time pass after 100% of Vout. Please correct.

BR