Hi

my customer test on our EVM with 5V DC source, no battery, no load on VSYS.

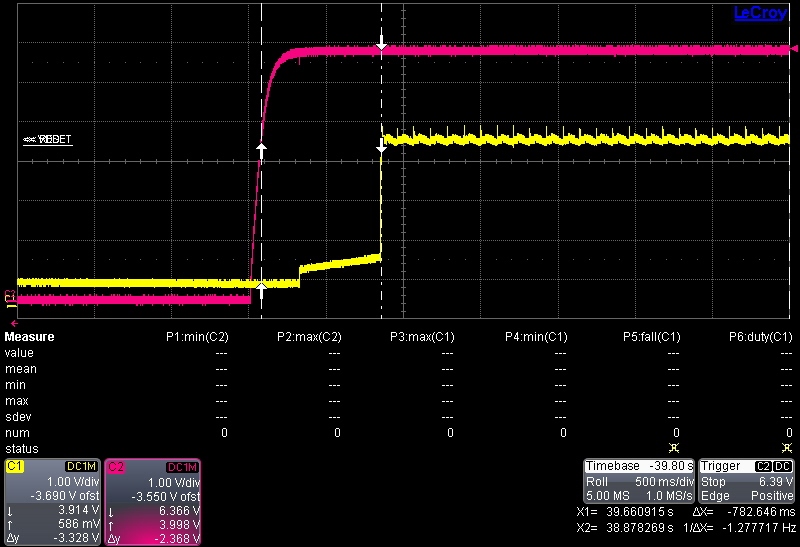

When D+ D- floating, the SYS will reach VSYSMIN about 0.78s later than VBUS reaches 5V. Shown below: (red-VBUS, yellow- VSYS)

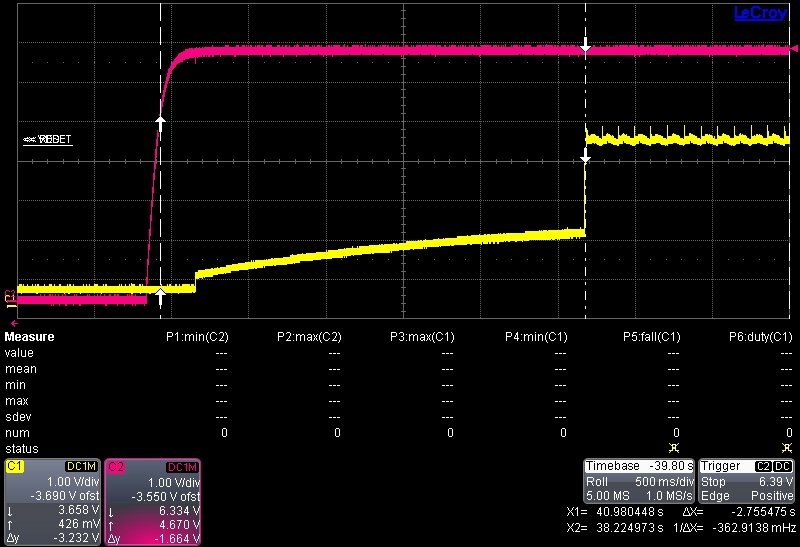

When D+ D- shorted, the SYS will reach VSYSMIN about 2.75s later than VBUS reaches 5V. Shown below: (red-VBUS, yellow- VSYS)

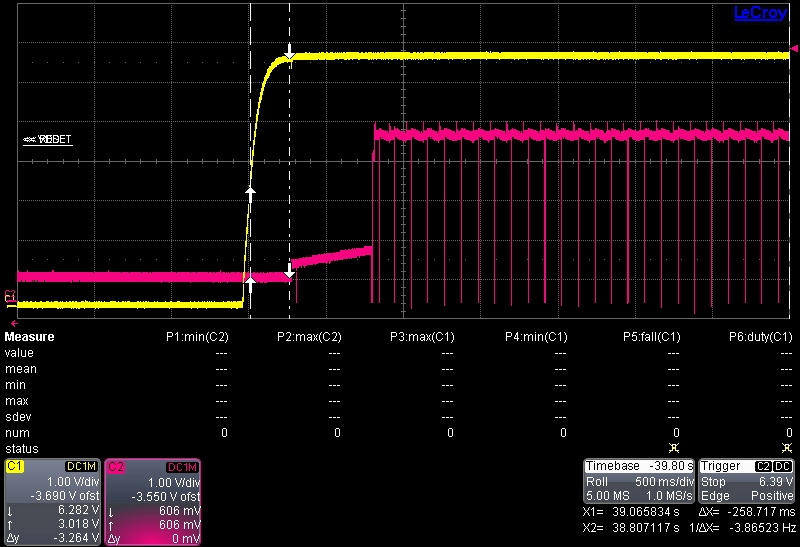

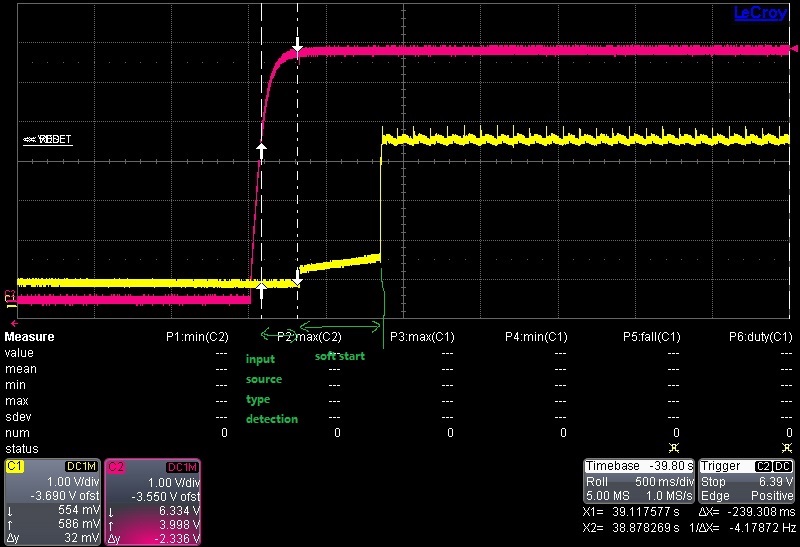

This should not be related to the process of INPUT SOURCE TYPE DETECTION because both converter started switching about 258ms later than VBUS reaches 5V shown below which means the INPUT SOURCE TYPE DETECTION finished within 258ms.

So the question is:

1. Why different D+ D- configuration lead to such a big difference of soft start time?

2. Which configuration can minimize the time?