Dear, Sir.

My customer is evaluation UCC21222-Q1 for their system.

At this time, They are asking following topics.

Please give your advice.

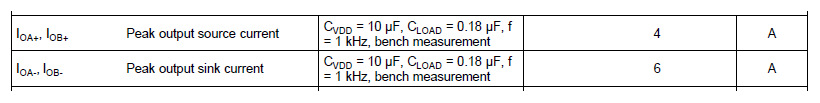

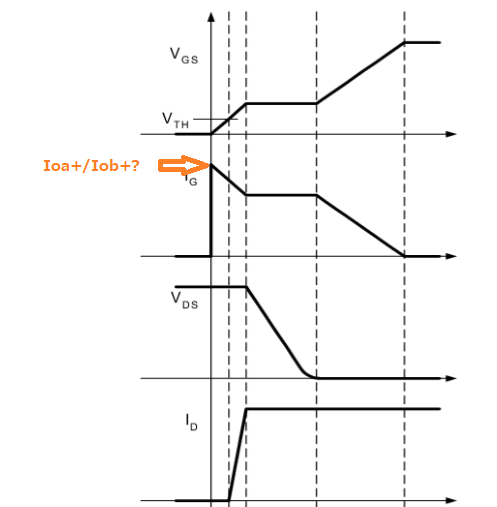

1. Source & Sink Current(Ioa+/Iob+, Ioa-/Iob-) are defined on the

datasheet as typical. To calculate the gate charging/discharging time

min/max would be significant, I think.

Is it possible to clarify min/max source & sink current?

2. What is the main factor to create above variation?

Accuracy of the internal current source?

3. I wonder Source & Sink Current(Ioa+/Iob+, Ioa-/Iob-) will keep

to complete the charging/discharging for Qg of external FET?

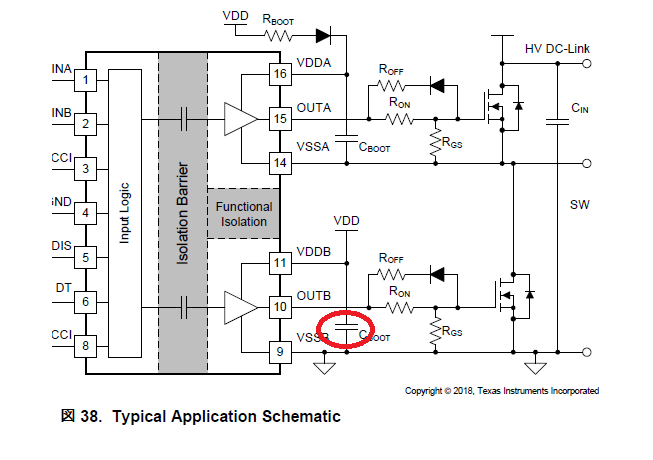

4. If Gate & Source was shorted on lowside FET(Source = GND),

Is there any damage on UCC21222-Q1?

Best Regards,

H. Sakai