Dear All:

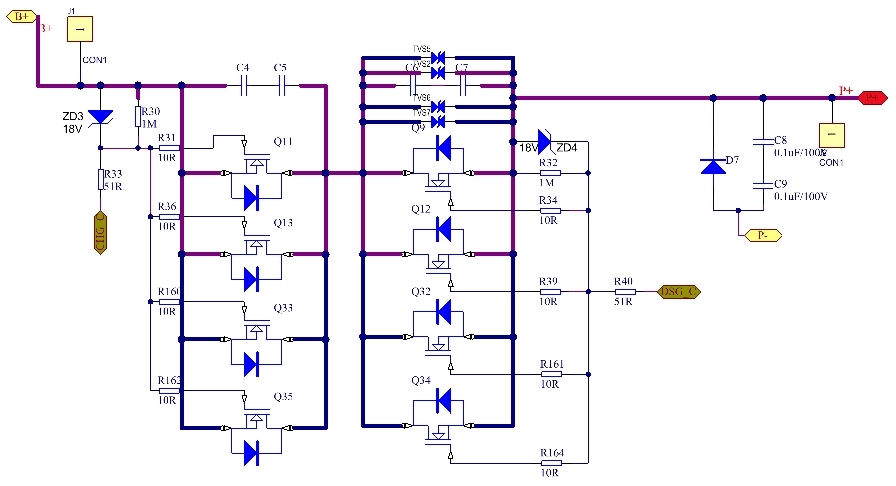

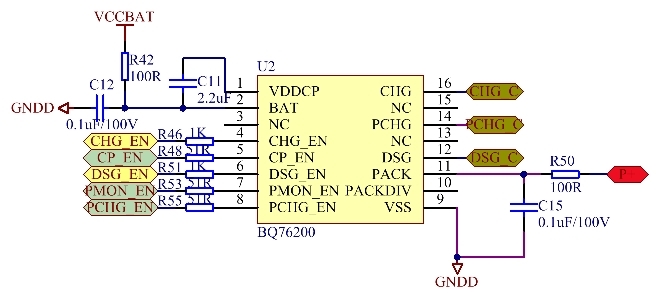

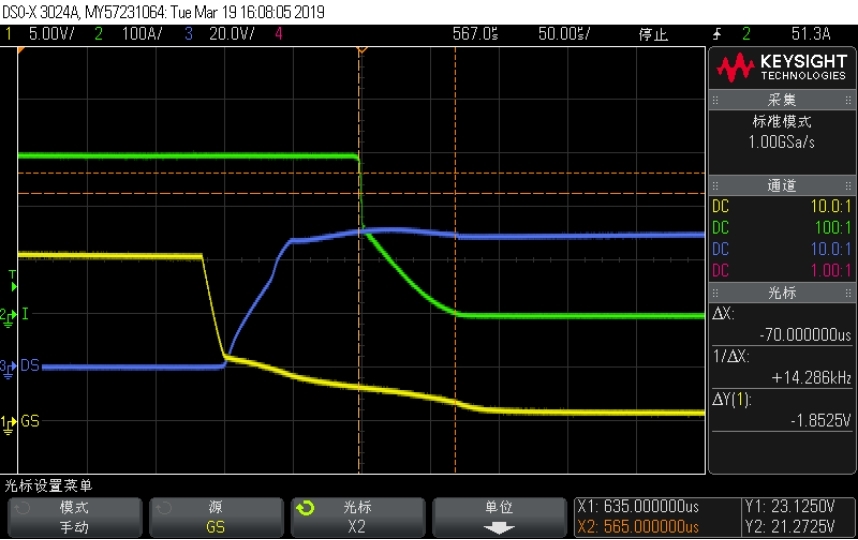

I use the BQ76200 to drive the High side mos in the BMS application, I find the discharge MOS is often short in the SCD test that the SCD current value is 1000A . As show below is the schematic and test wave. I find the Miller platform time is too long. Can you help me to solve the issue , Thanks~