Other Parts Discussed in Thread: TPS65217,

Sitara Friends & Family,

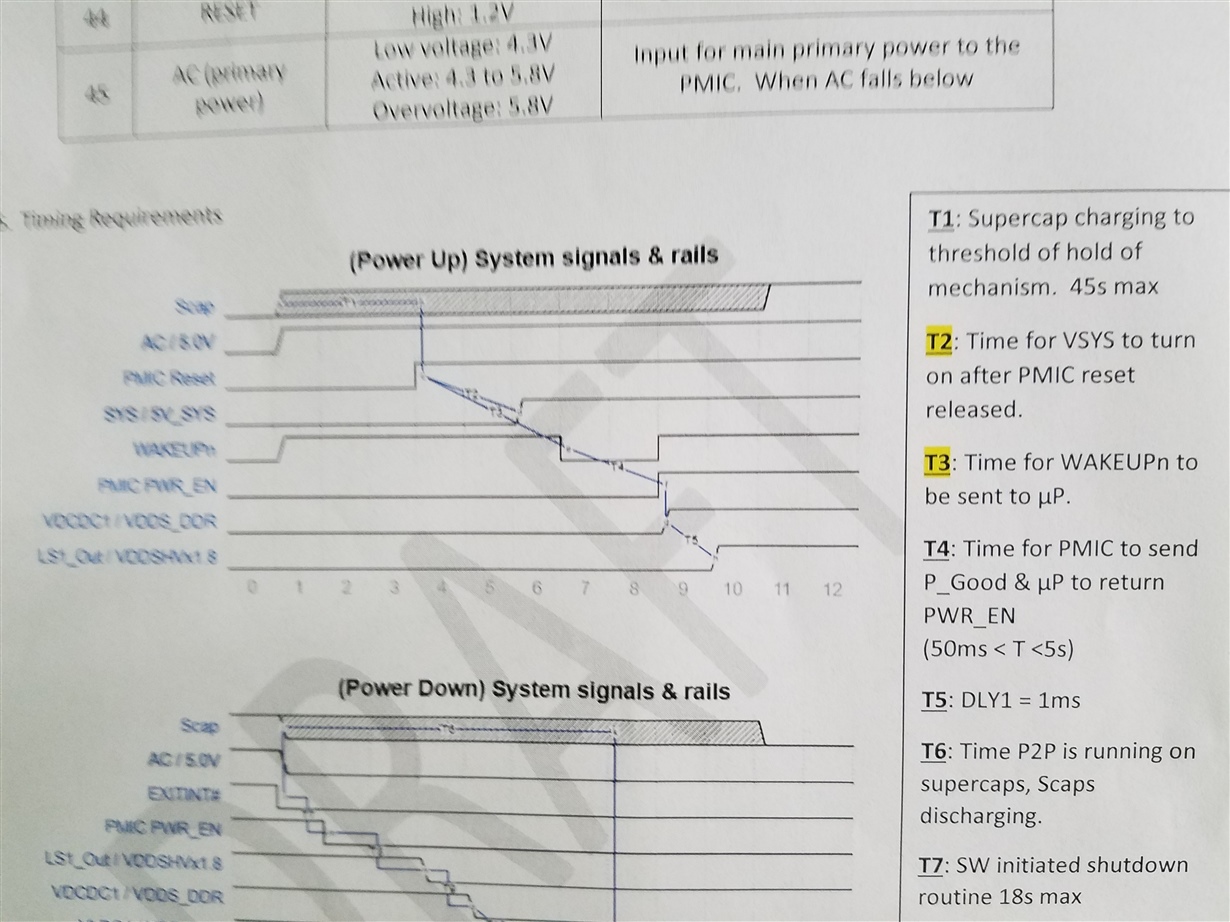

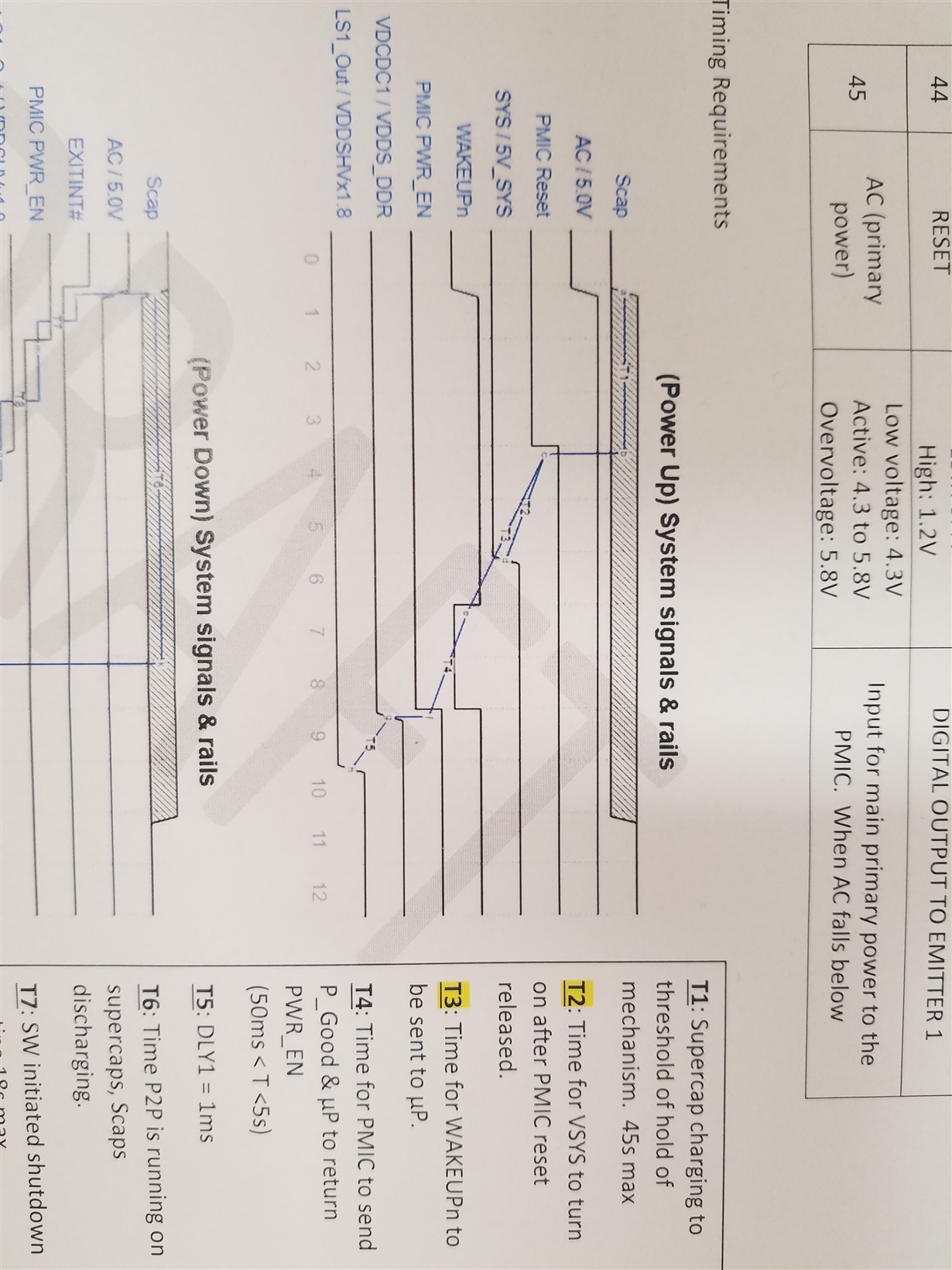

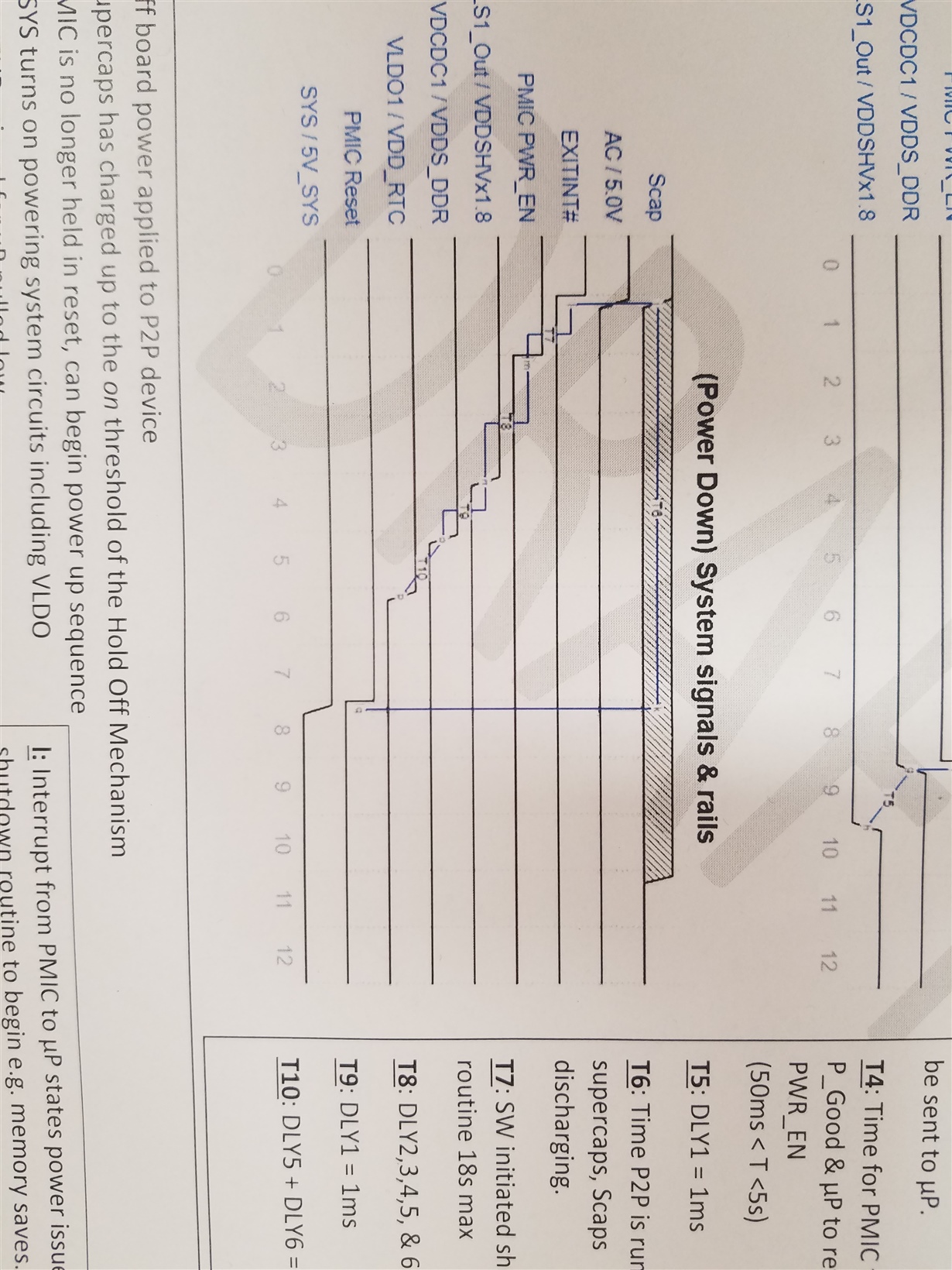

Our customer has a question regarding Timing Specifications between our AM335x Sitara and corresponding TI PMIC (TPS65217). See the below graphic which contains timing info per our specifications for most parameters, EXCEPT for that listed for T2 and T3:

Can we offer a Timing Spec like we do for some of the other parameters (T1 T4 etc) such as 50msec < T < 1 Sec) for instance?

Also, please confirm that the nmi_int register location is indeed : 9C0h as defined in AM335x TRM.

TY,

CY