Using the Automotive 1-kW 48-V BLDC Motor Drive Reference Design (TID-00281) as a reference, I have used the same circuit for the gate drivers and H-Bridge to design my own PCB for a 2 phase BLDC 48V motor.

During testing, 3 gate drivers (UCC27201A) have failed on 5 boards. The gate drivers are supplied with 12V using an isolated DC-DC converter with a 500mA output (Traco TEN 6-2412WIN).

When the gate driver fails, the 12V supply of the DC-DC converter is pulled down to a few volts, the failed gate driver seems to overload the 12V supply.

To find the faulty gate driver, I measure the resistance across the GATE and SOURCE of each MOSFET.

The resistance should be around 10k, which is the resistor across the GATE and SOURCE of each MOSFET.

However, where the gate drivers fail the GATE and SOURCE resistance is much lower (between 10R to 100R).

When I remove the faulty gate driver from the board, the output of the DC-DC converter returns back to 12V.

The gate driver failures are random and have failed for:

- Phase A or phase B

- Limb A or limb B

- Top or bottom switch

What would cause these gate drivers to fail ? Other than the PCB layout, the circuit is the same as the TI reference design.

If the answer is not obvious, then how do I go about diagnosing what causes them to fail ?

Attached is a PDF for the schematic and PCB layout (4 layer, 3oz copper on all layers).

I have omitted the schematic and PCB design for the 48V filtering, DC link capacitors, 12V filtering etc as the circuit is the same as the reference design.

Other than the PCB layout, the only difference between the TI reference design and my design is:

- Traco DC-DC converter used for 12V isolated supply (I needed higher current to supply a control board)

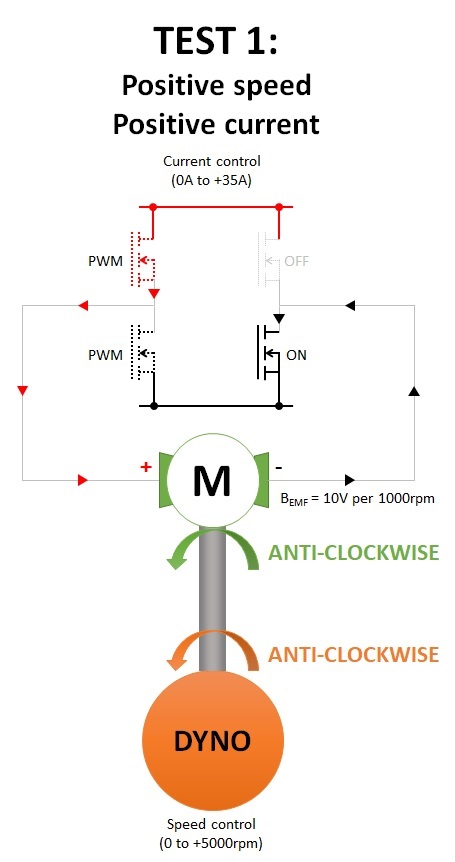

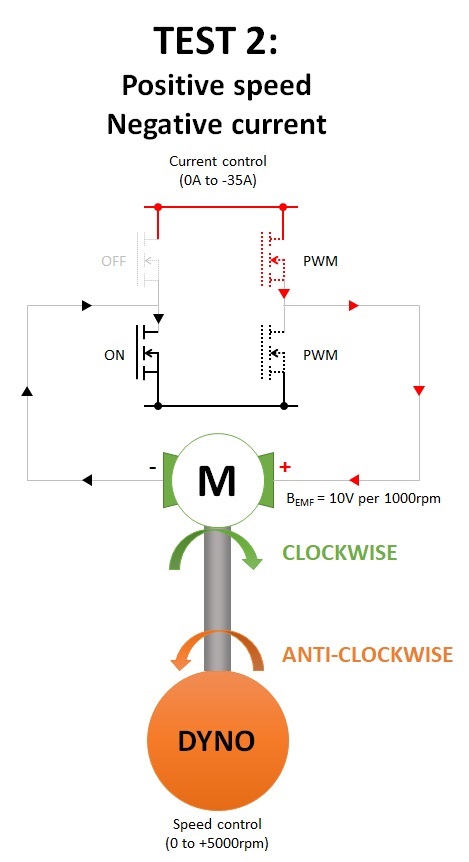

- 2 phase (four full H-bridges) instead of 3 phase (3 limbs)

- Equivalent through hole MOSFET instead of surface mount