Dear experts,

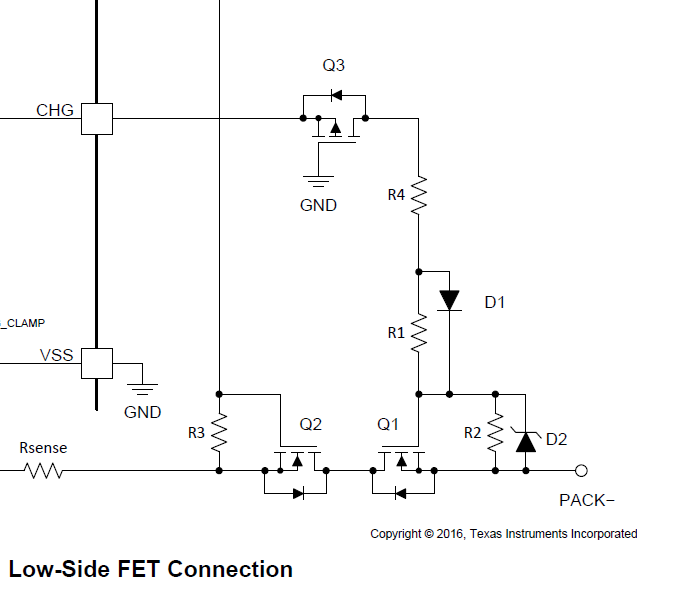

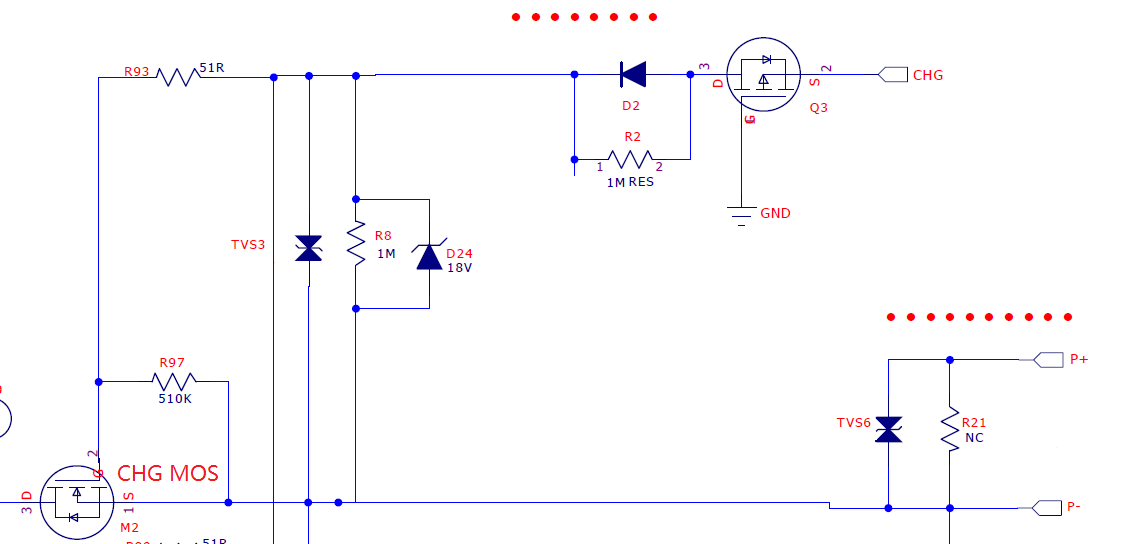

Our customer noticed that there is a problem in our low side CHG and DSG driver project . The attached file is our schematic, we followed the connection in bq76940 datasheet. And we also noticed some reference design adds a 1k resistor R4 between CHG pin and CHG mos gate (as below), I wonder what the effect of this 1k ohm resistor is and can this resistor be ignored (now the customer sets R4 0 ohm).

Our problem is when CHG and DSG mos off, the pack still has voltage on it when we measure it with multimeter. And some end customers thought it's dangerous. After testing, customer found there is leakage current on the line between CHG pin and CHG mos gate, about 20-30uA. When customer disconnected this line by taking off 0 ohm R4, the voltage disappeared.

Could you help us to solve the problem and tell me the effect of R4 resistor? Thanks a lot.