Other Parts Discussed in Thread: UCC28630EVM-572

Tool/software: WEBENCH® Design Tools

Hello,

We are currently using UCC28634DR flyback controller for a closed-loop control in a flyback project (Vin = 240VAC, Vo = 12VDC, Io = 0.5A). We are using the Webench design shown below. All the components we purchased are the recommended in the diagram except for the transformer which we hand-made (ratio = 1:7 for both secondary and auxiliary).

The project works successfully as an open-loop when we provide the switch pulses from a microcontroller and the outputs in both the secondary and auxiliary sides are 12VDC. The off-state voltage spike is only 465V. This open-loop test indicated that the transformer and the switch were working properly. However, every time we run the circuit using the UCC28634D with the configuration below, the switch (600V,16A MOSFET) gets damaged (shorted). We even used a snubber circuit (R= 4.7K, C = 10nF) in addition to the recommended clamp diodes and the mosfet still gets damaged.

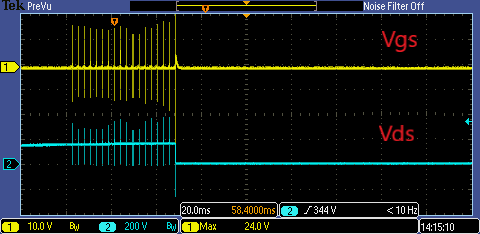

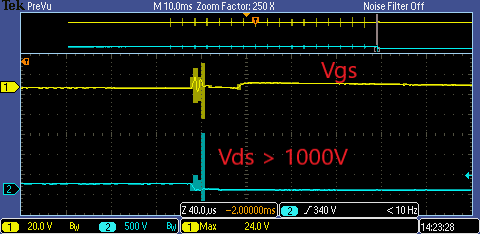

We debugged the circuit using DC input (330VDC) instead of the mains. We saw that when the HV pin in the UCC28634DR is above 40VDC, there are weak pulses established in the mosfet gate but VDD is still 0V. Once we slowly increase the input voltage to 200VDC, the mosfet gets damaged with huge Vds spike (above 800V).

We believe that UCC28634DR to some reason, is not providing the initial pulses to the switch the MOSFET in order to create the auxiliary output to start the functionality.

We would appreciate a help if the configuration below is applicable to our project or not. And why the mosfet is failing at higher HV input than 200V.

Thank you