Hi,

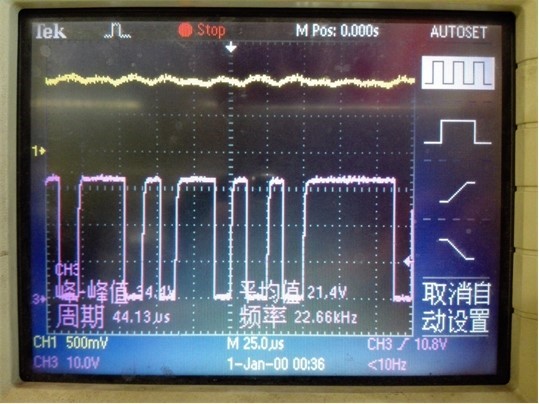

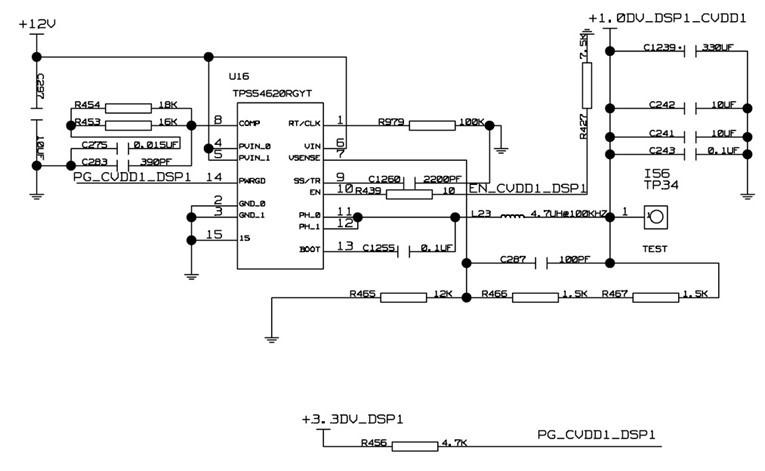

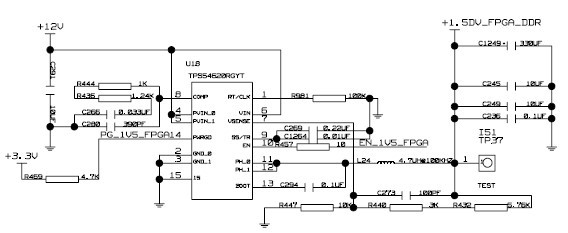

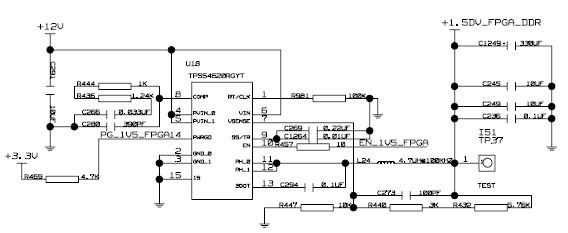

The enterprise network power project has the following problems when using the TPS54620 power chip:

Two boards appear, using TPS54620 chip, 12V input, 1.0V output, start working normally, after working for a period of time, re-power-on reset, the board works abnormally.

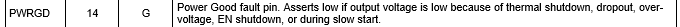

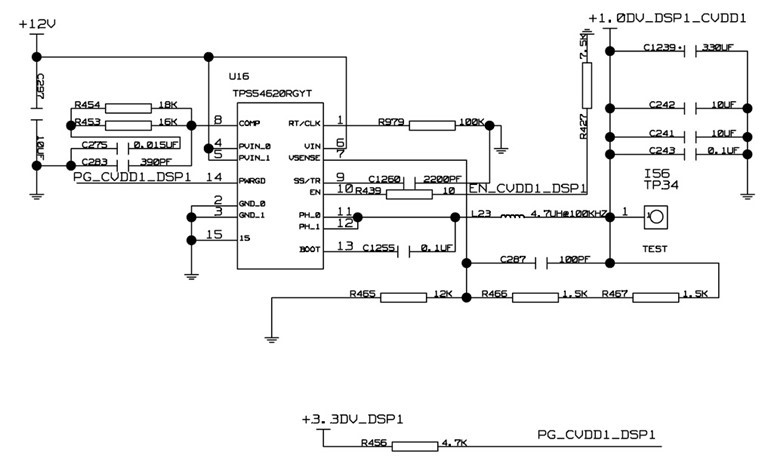

After testing the board, the 1.0V output of the TPS54620 is normal, but the output of the POWERGD status pin is constantly changing, resulting in abnormal monitoring of the status of the pin.

Why does the chip status pin have a constant transition? How to solve this problem?