Hi,

When we tested the case of power down for TPS7B7033, there happened an issue about Vout ”MEM_3V3” as followed.

-

Background

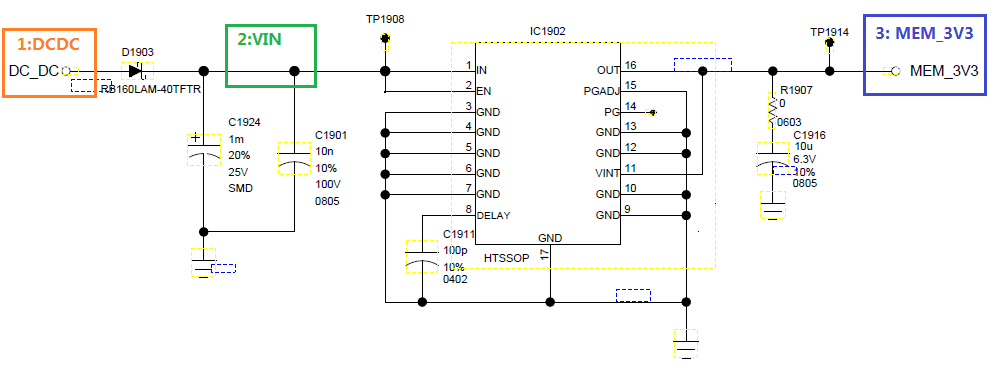

TPS7B7033 is a LDO for the MCU as a constant power. As the schematic is shown in the below picture, DCDC is sourced from battery(14V), VIN is the input supply for TPS7B7033 which is isolated with DCDC by a diode, while MEM_3V3 is 3.3V level output power from TPS7B7033, which powers for the MCU constantly. EN of TPS7B7033 is the same net of VIN.

-

Issue

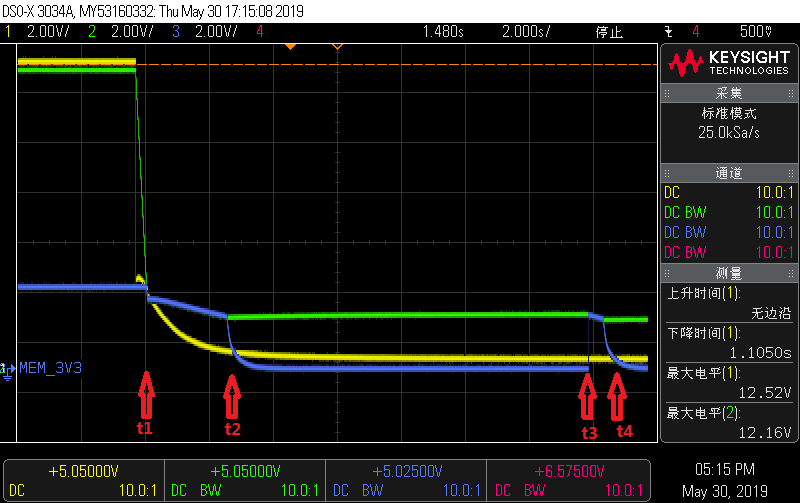

When powering down the DCDC, we found that the MEM_3V3 went to 0V slowly, then would go up to about 2V strangely after several seconds, a lasting about 440ms pulse is shown in the below waveform.

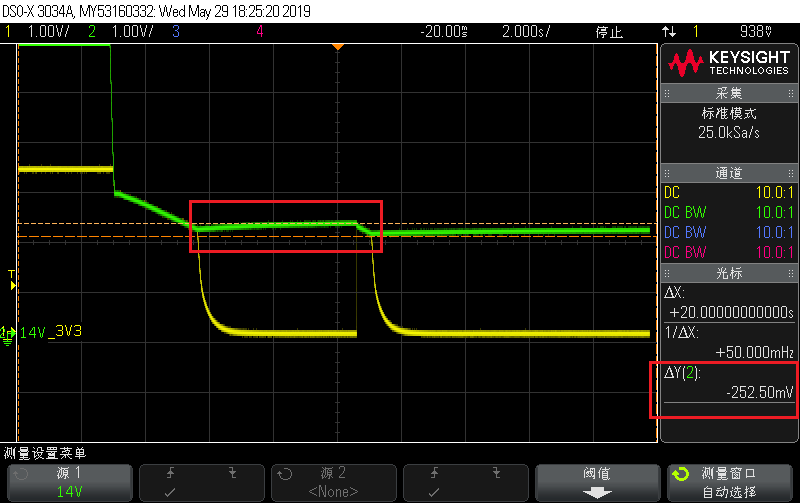

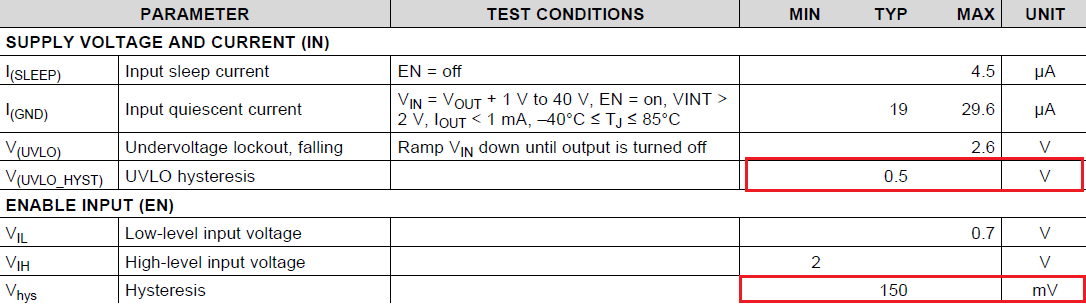

Power down happened at t1, VIN is followed by MEM_3V3 between t1 to t2, then MEM_3V3 is shut down because the EN pin is disabled at t2. From t2 to t3, why does VIN rise slightly about 150mV at t3 which triggers the EN of TPS7B7033, and then MEM_3V3 follows the VIN again as a pulse? At t3, DCDC goes to almost 0V, so VIN is isolated and can’t be charged by DCDC, My question is: Where and why leads to the VIN rising?

(Note: Probe1 is DCDC marked yellow, Probe2 is VIN marked green, Probe3 is MEM_3V3 marked blue)

Do you have any comment on it? Thank you and wait for your reply!