Other Parts Discussed in Thread: TPS65130,

Hello,

I am currently using a TPS65130 for one of our designs, to generate +/- 5.5V rails (to be exact R300 is actually 47k to have 5.5V, but not relevant for the issue). here schematic of my implementation:

We are currently doing some initial EMI compliance testing and it's failing to pass due to heavy spikes related to this converter.

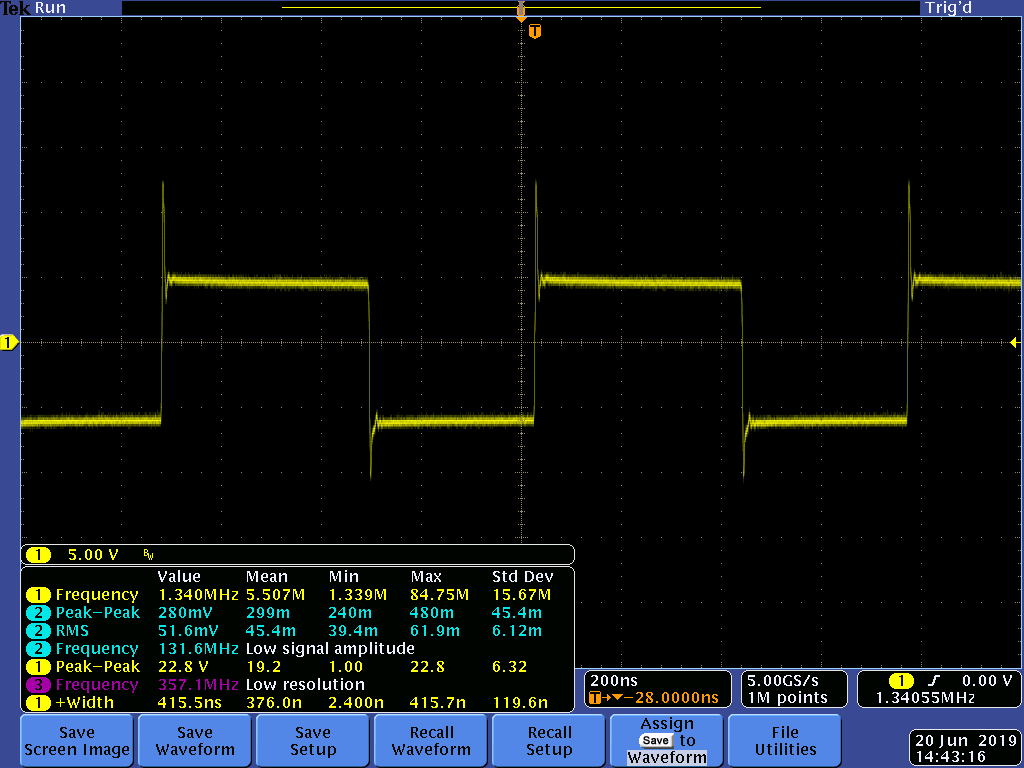

All the spikes in the graph are 1.3 MHz apart, which is the switching frequency of the TPS65130. I can disable the converter and all spikes disappear.

I started investigating by probing the switching nodes for the positive and negative outputs (Pin 13-14 for negative, pin 1-24 for positive). I noticed very high switching spikes on the negative side while switching. The positive spikes are higher than the negative.

I tried changing diodes, changing compensation caps, inductors: no difference at all.

I took a step back and went on the evaluation board TPS6513xEVM-063 (which uses a TPS65131 instead), with all original parts apart from:

- Q1 bypassed

- diodes are now MBR0530T3G

- output voltages set to +/- 5.5V

- connected a 20 ohm resistive load between GND and VNEG output

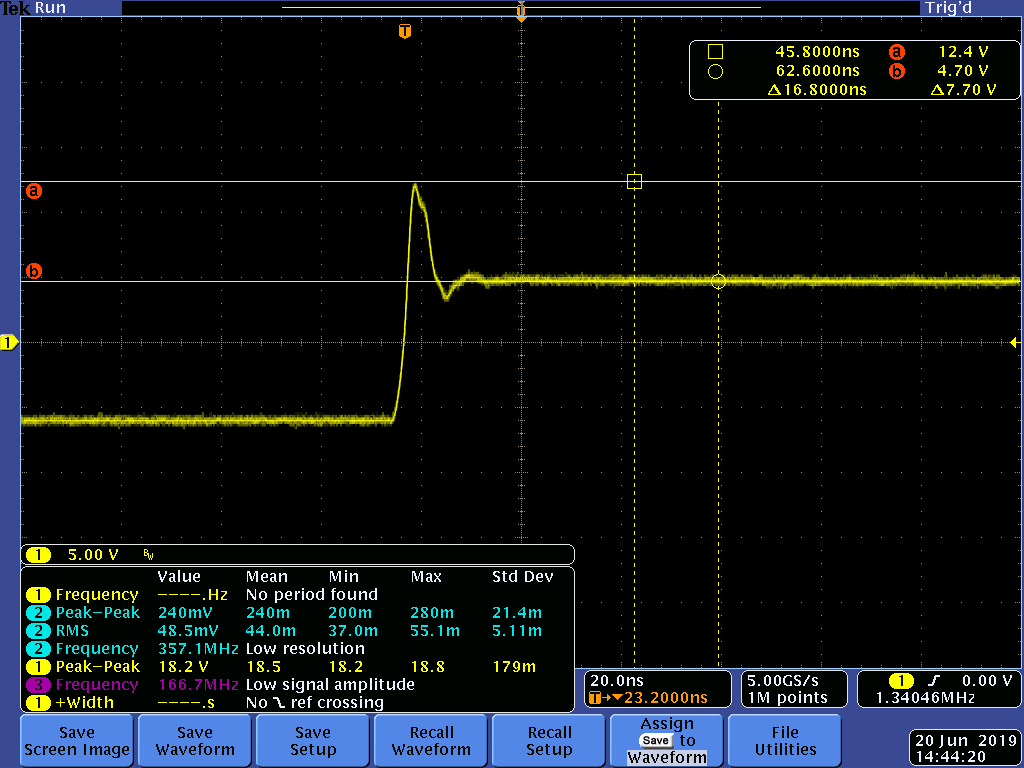

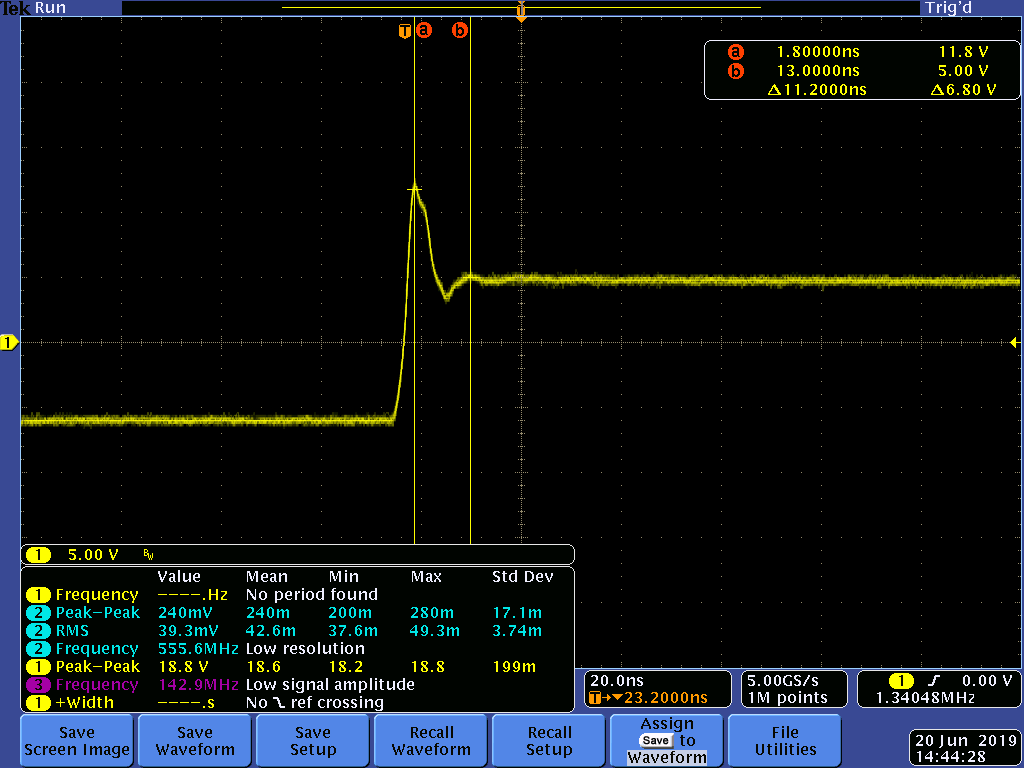

This is what I get when probing across L2, (DC coupled, 250 MHz BW limit, ground coil around the probe tip):

As you can see the positive spike is overshooting by more than 7V. I believe this is the cause of the EMI problem I am experiencing. Given that this behaviour happens already on the evaluation board, it doesn't look promising.

I tried to add some RC snubbing across the diode OR across the inductor (100pF series with 5 ohm, in both cases), with no difference whatsoever in the result.

Just want to point out that my product scope images look exactly the same, same spikes.

Any recommendation on what to try to fix this? I'd like to see the fix working on the evaluation board first, so please ignore in first instance my implementation.

If there's no way to fix this behaviour we'll be forced to move to another converter/topology as this won't pass regulations.

Many thanks,

Matteo