Other Parts Discussed in Thread: AM5716,

Hello,

On my board I have a SItara AM5716 and its PMIC TPS659162RGZR.

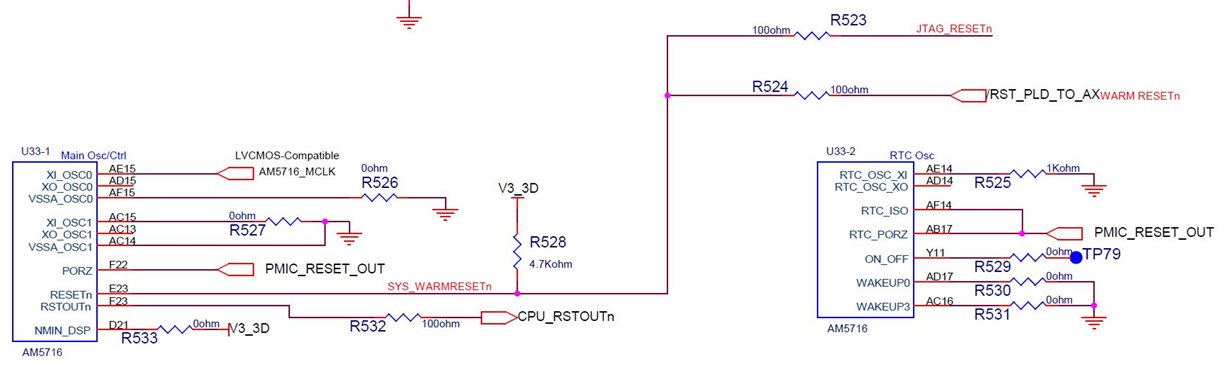

Below I show the schematics about PMIC

and reset section of Sitara

AM5716_MCLK is a 20MHz clock and SYS_WARMRESETn is high.

For the connections I followed the Figure 2 of "TPS65916 User's Guide to Power AM571x (SLVUA04D)".

The PMIC RESET_OUT (net PMIC_RESET_OUT) and CPU RSTOUTn (net CPU_RSTOUTn) are always low (all the power supply of the PMIC are correct and the PMIC POWERGOOD is high)..

I put a 4.7Kohm to pull-up the PMIC_RESET_OUT and the behaviour of this net and CPU_RSTOUTn are the following:

From the datasheet of the PMIC (SLVSD09B –MARCH 2016–REVISED MARCH 2017) in the paragraph 5.3.4 Device Power Up Timing, I read: "If the time from VCC to VIO is less than 6 ms, the VIO buffers will be supplied while the OTP is still being initialized, which could cause glitches on any VIO output buffer. Supplying VIO at least 6 ms after supplying VCC ensures that the OTP is initialized and output buffers are held low when VIO is

supplied."

So I connected VIO_IN to V3_3D which is up 26ms after 3.3V, but nothing changed.

All the power supply are correct even though VIO_IN is connected to 3.3V which is the VCCA power supply of the PMIC.

Can you help me with this issue?

Thank you

Best regards

Francesco