Other Parts Discussed in Thread: LM3421

Hello,

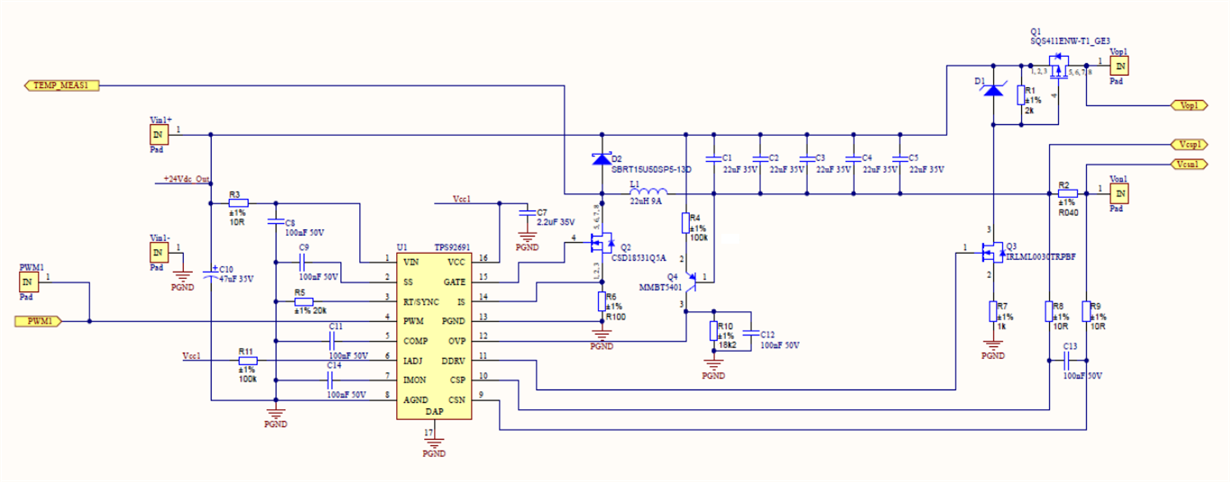

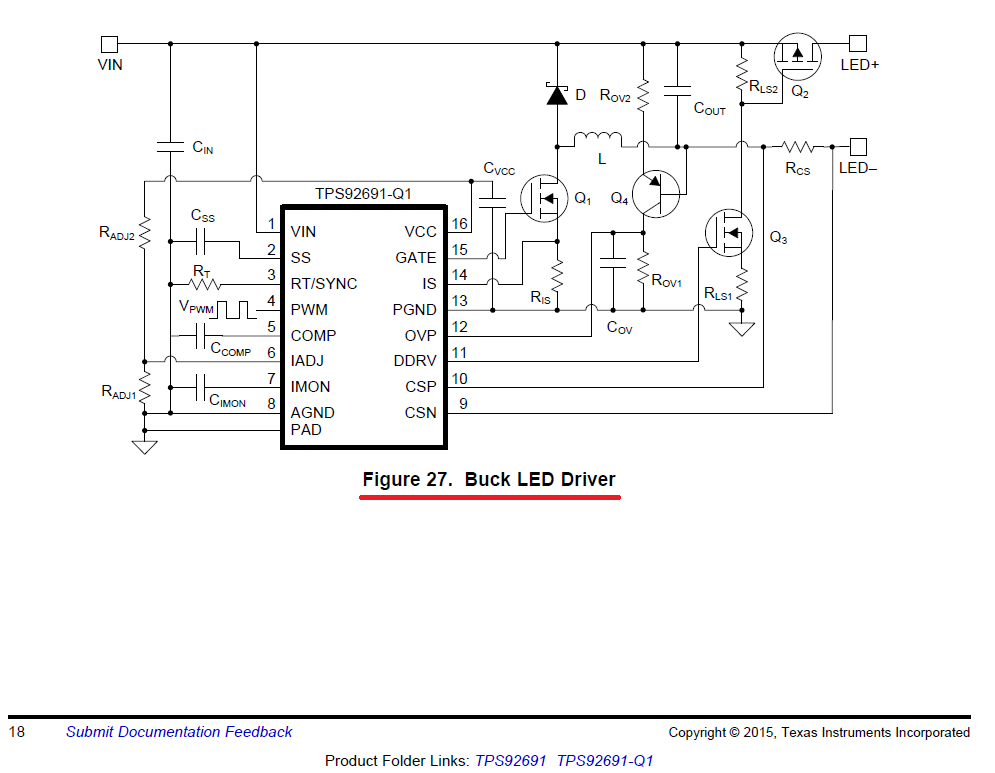

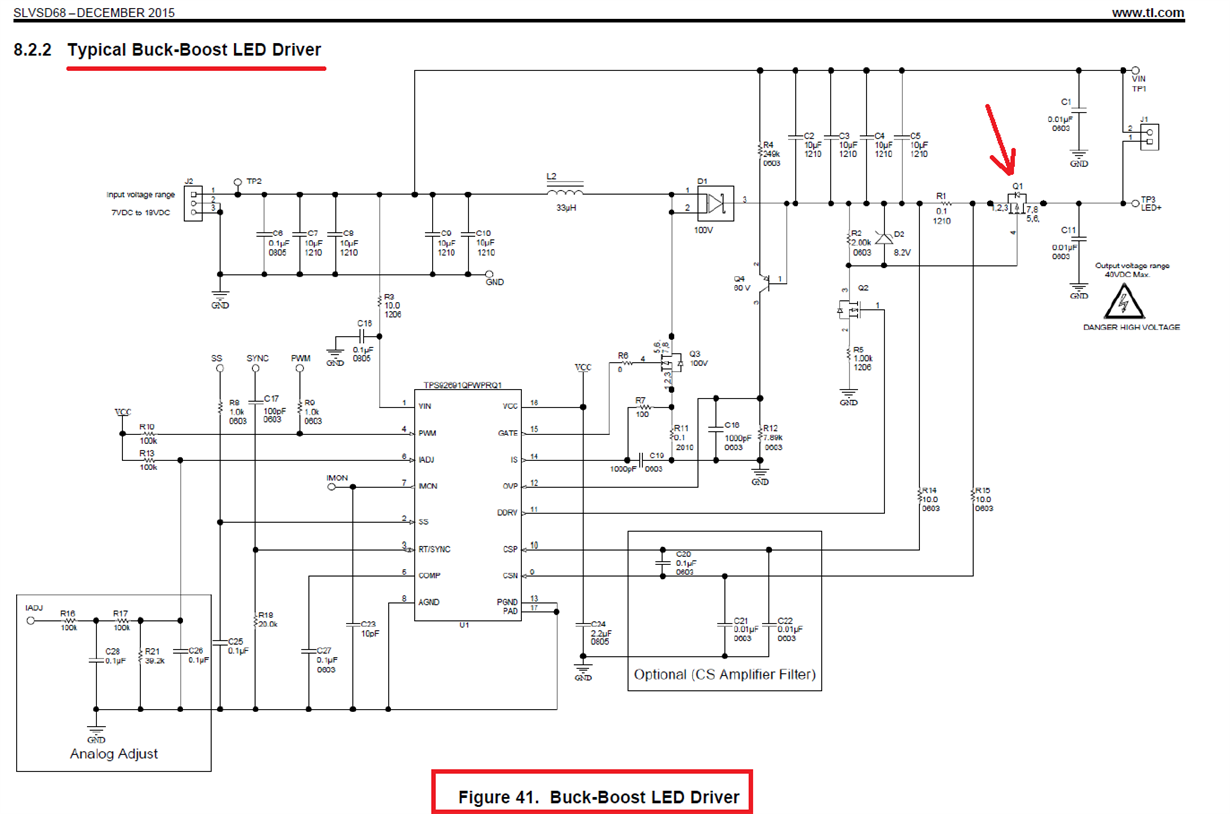

I have designed and performed a low-side buck converter with the aid of TPS92691 part (schematic attached).

Vin = +18V to +26Vdc, Vnom = +24Vdc

Vo = 5Vdc (that is the Vf tipycal led value used as a load)

Io = +4.5Adc.

The fact is that after starting up process the led is not lighting and the converter seems to be off. I just see a few miliamperes in the input power supply.

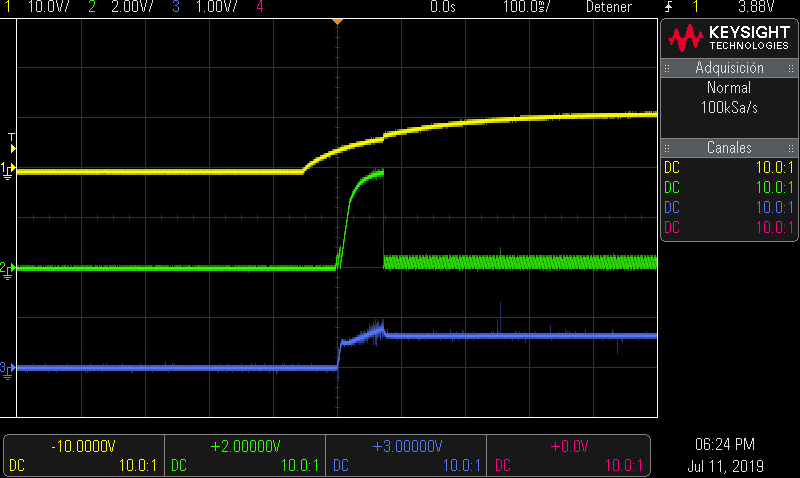

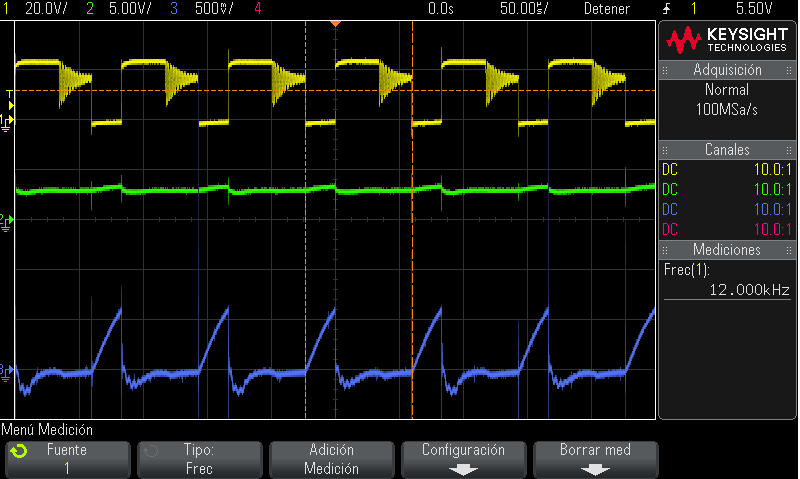

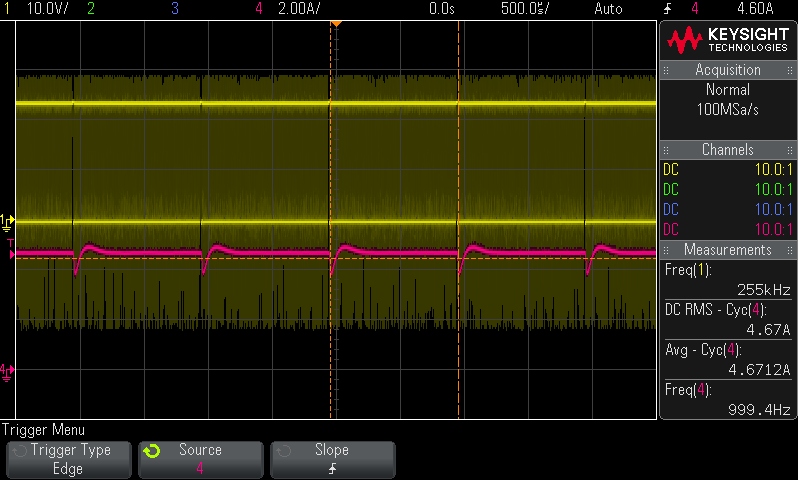

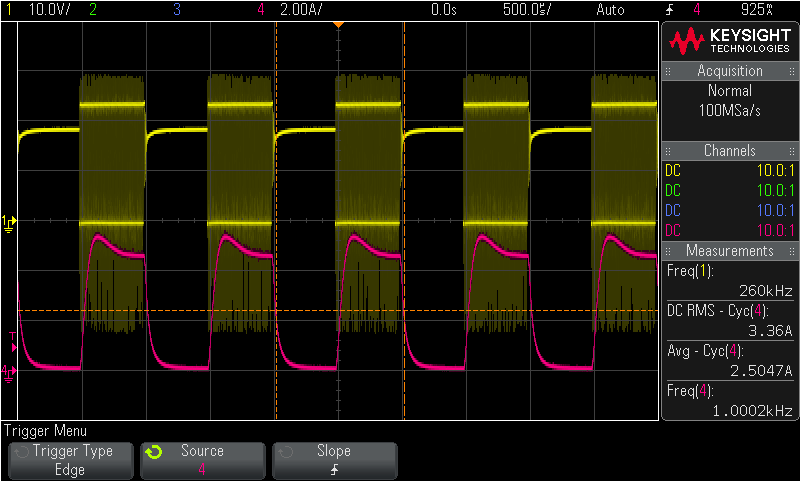

I attach one capture of the oscilloscope, where Ch1 is U1-1 pin (Vcc), Ch2 is U1-2 pin (SS) and Ch3 is U1-12 pin (OVP).

Ch2 (SS) is cut after 75 ms aprox. and it starts to oscillate, the OVP signal is under 1,24V (Vov is almost 8V by design) and it is so far from the limit level.

I cannnot connect 24V to the input because after 10V the converter behaves in such a way and I cannot provide more than 0.7A to the power supply because of this issue.

I am providing either 1KHz pwm dimming signal, 5V or pullin-up with a resistor 100KOhm the PWM pin, which is the case of the capture I attached. The result is the same in both cases.

So, what is happening here? As the led voltage (Vf) is 5V and voltage input is just 10V I can't even see Vsw node operating and the converter seems to not operate really well. In fact i cannot state that the converter is really turned on.

Is there any other protection that is been activated and so this behaviour is justified? I checked the datasheet and saw OVP at starting up process but do not know if there is something else here.

Please, any idea? Could you help me please?

Regards,