Other Parts Discussed in Thread: LM5045, UCC25600, UCC28951,

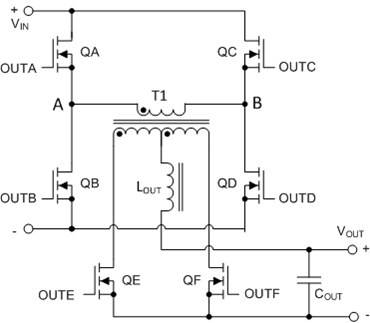

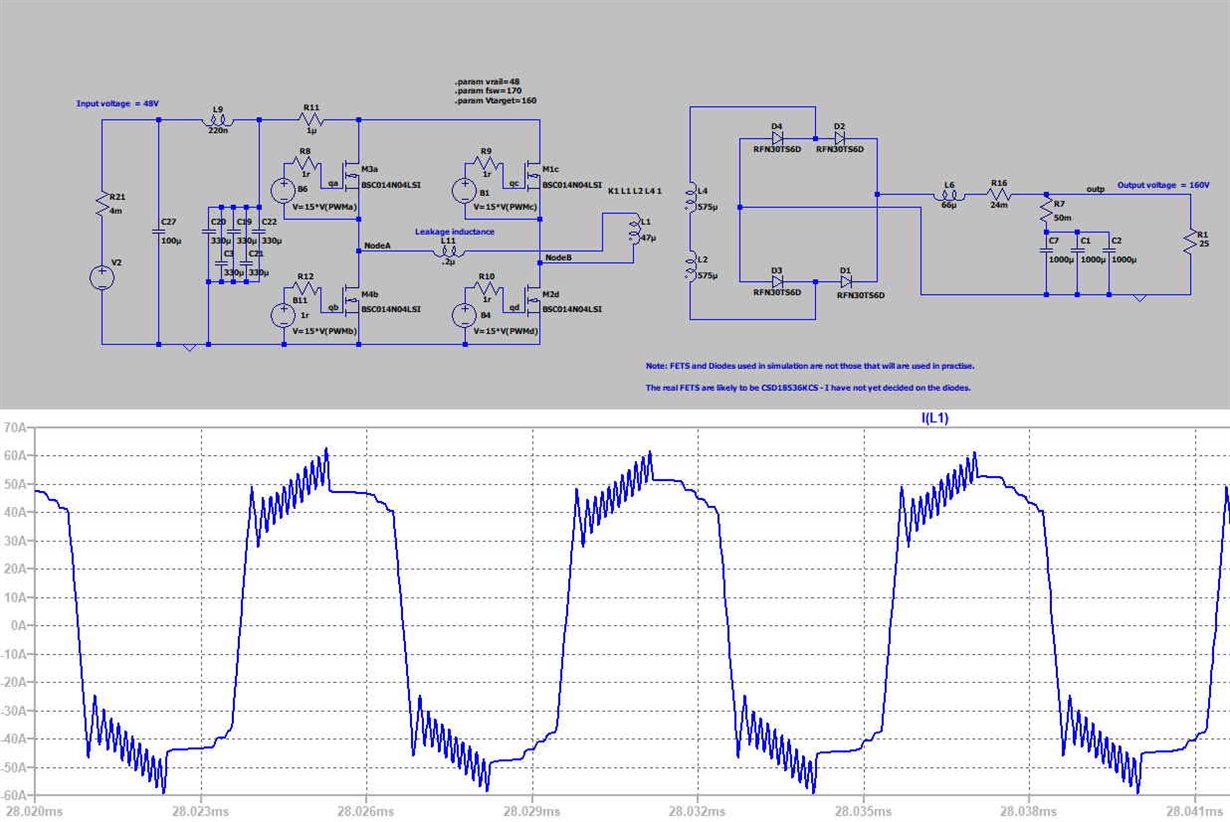

This is my first phase shift full bridge project and I am having some trouble understanding how low-loss switching is ensured when bridge FETs turn off. Especially in the passive leg, when the circulating current is at it's peak. I can find no explicit mention in the literature (maybe I'm missing it) - although much seems to be made about turn-on. Is it simply the capacitance at the leg middle node holding the voltage while the current through the FET drops? In which case the capacitance needs to be large enough to soak up the circulating current without the voltage rising significantly for the Tf duration of the FET.

My problems are probably made worse by the fact that my converter is 500W+ running from a 24V source, so the currents are absolutely huge - so if any has any suggestions for a more appropriate topology (must be isolating), then that would be appreciated.