Hi Team,

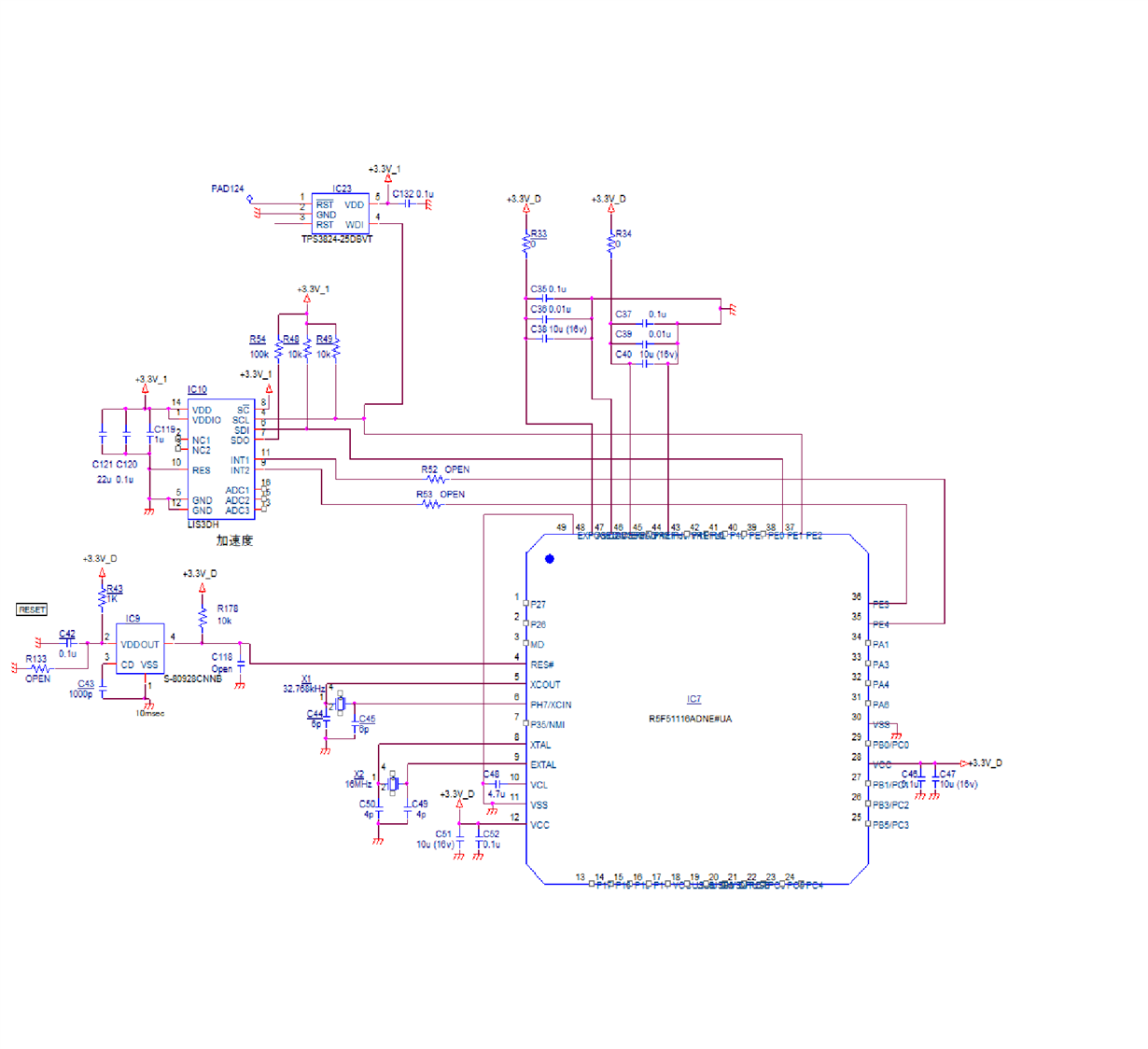

We are applying TPS3824 to our design.

I have some questions about how it works.

1. WDI signal is asserted when power up sequence, /RESET is still "Low" output.

2./RESET becomes "High" after td.

3.A 3.3V pulse(240msec) appears from the 2.7V(2sec) output of Sequence / RESET.

4./RESET becomes "Low" after the pulse.

5./ RESET is always low even if the WDI signal is asserted.

question1: Is the WDI pin at 3.3V pulse high impedance?

question2: Why does /RESET not becomes high when WDI asserts?

Regards,

Otsuka