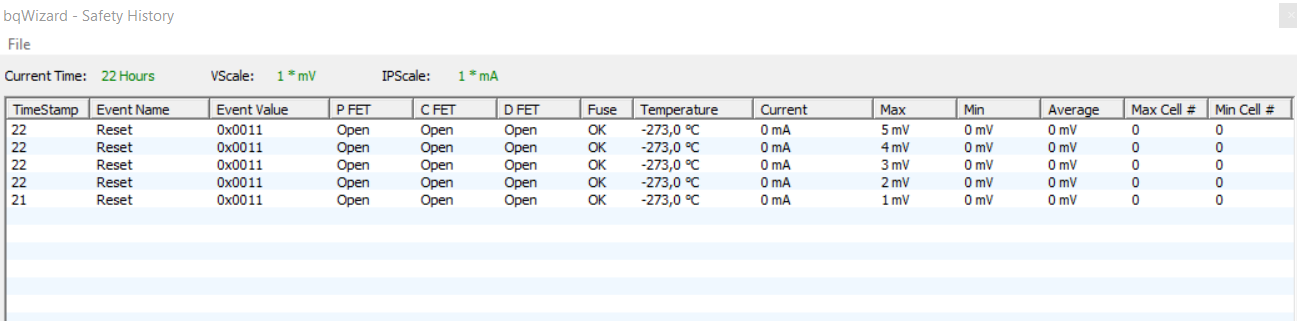

During EMC testing (Immunity test) we experienced multiple device switch-off due to power loss. Power returns back in some seconds. Only reset events with value 0x0011 have been logged. If we manually reset the BMS chip, reset event with value 0x0041 is logged and current time is set to 0. What is the reason for reset 0x0011 and how it is triggered?

Alex