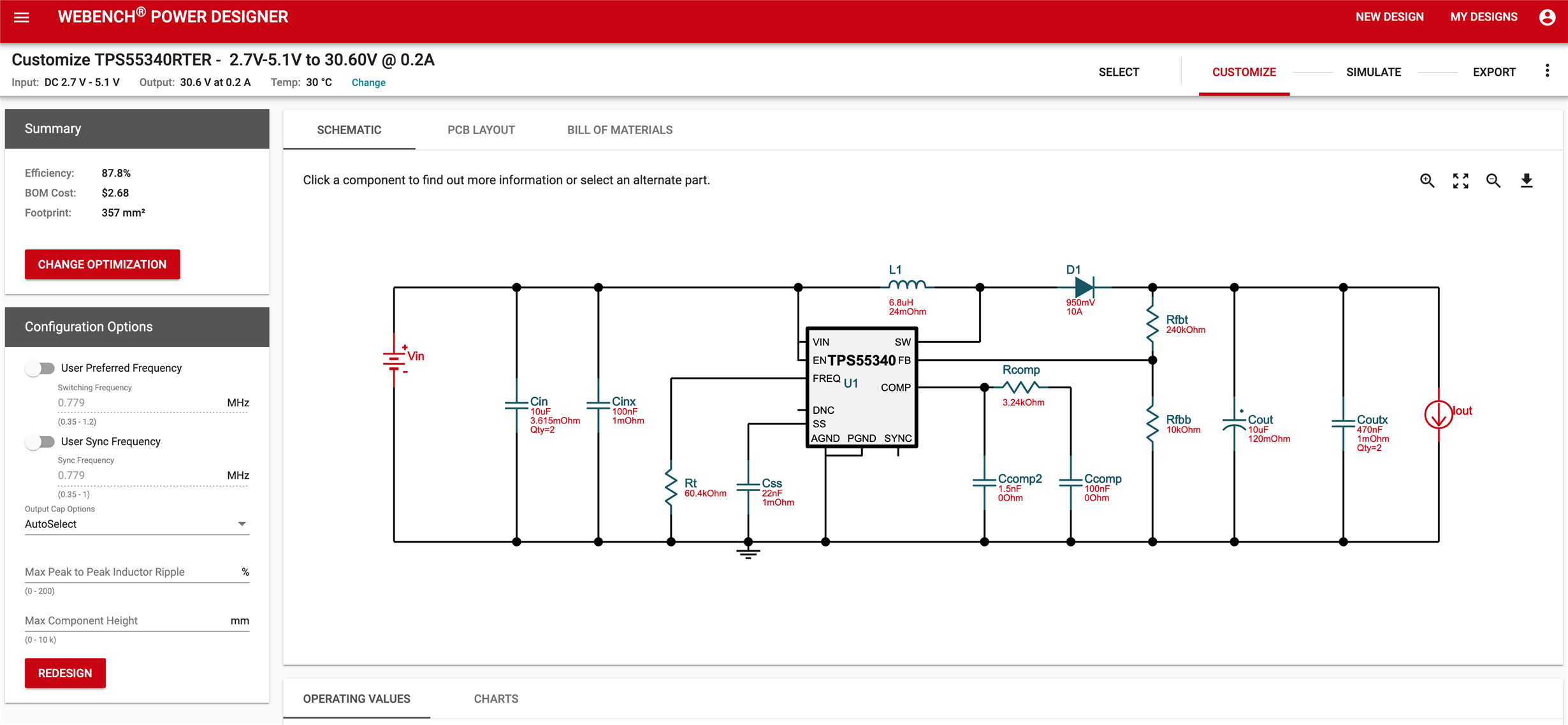

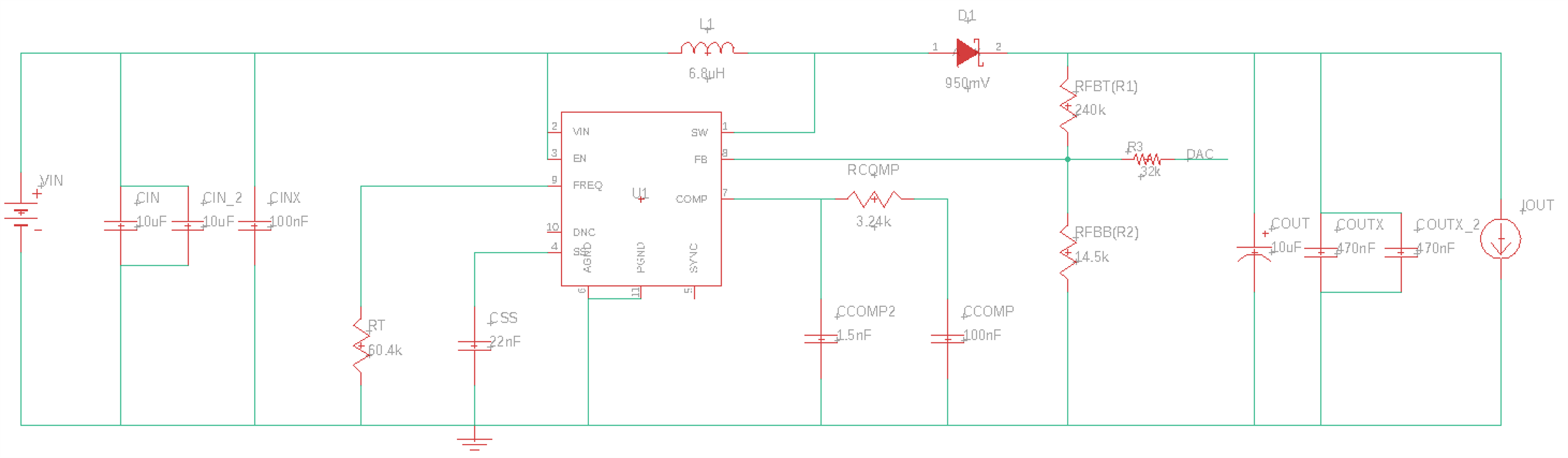

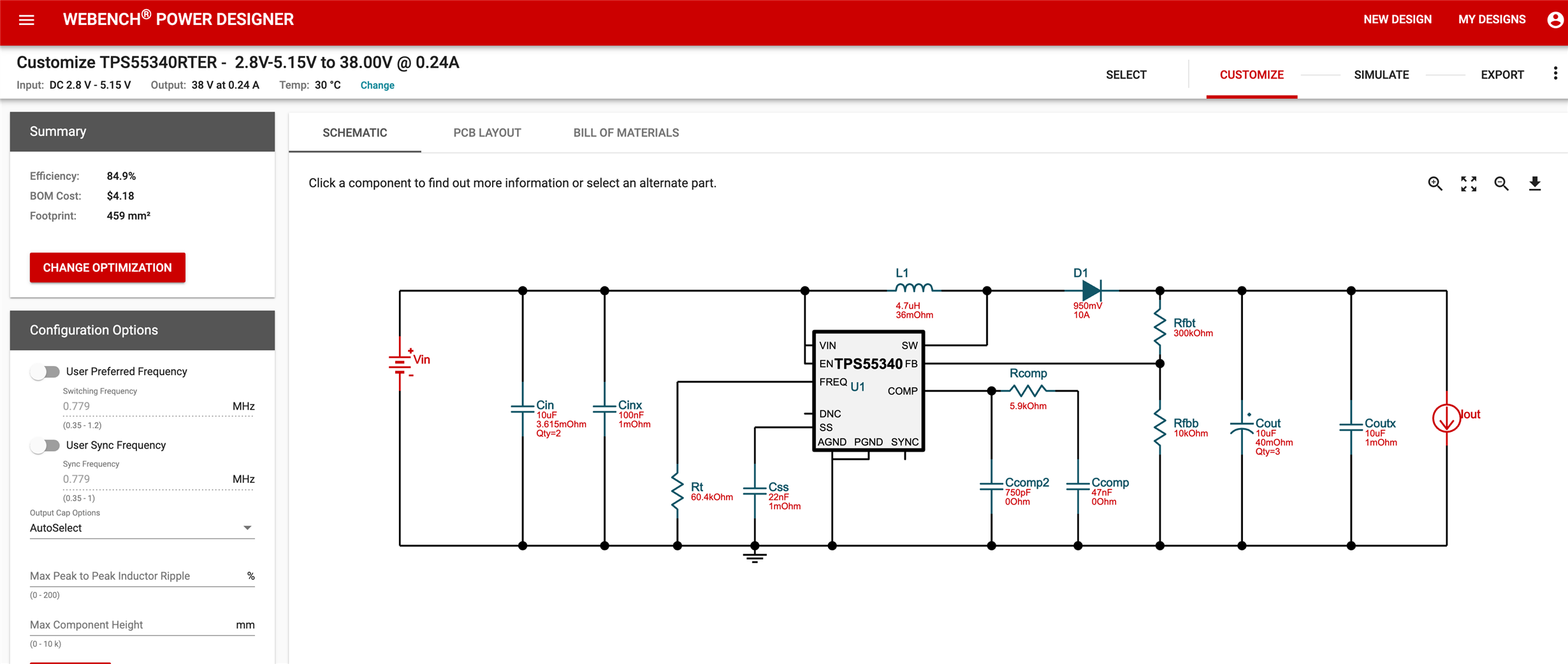

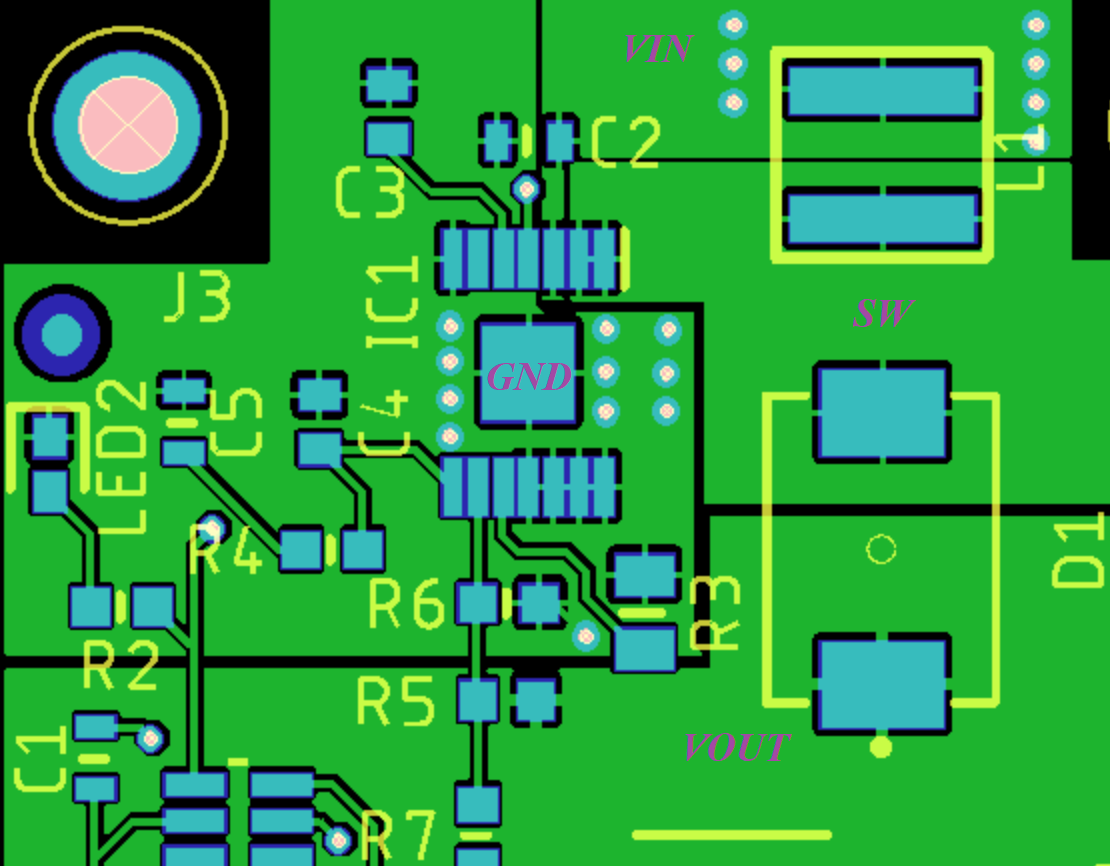

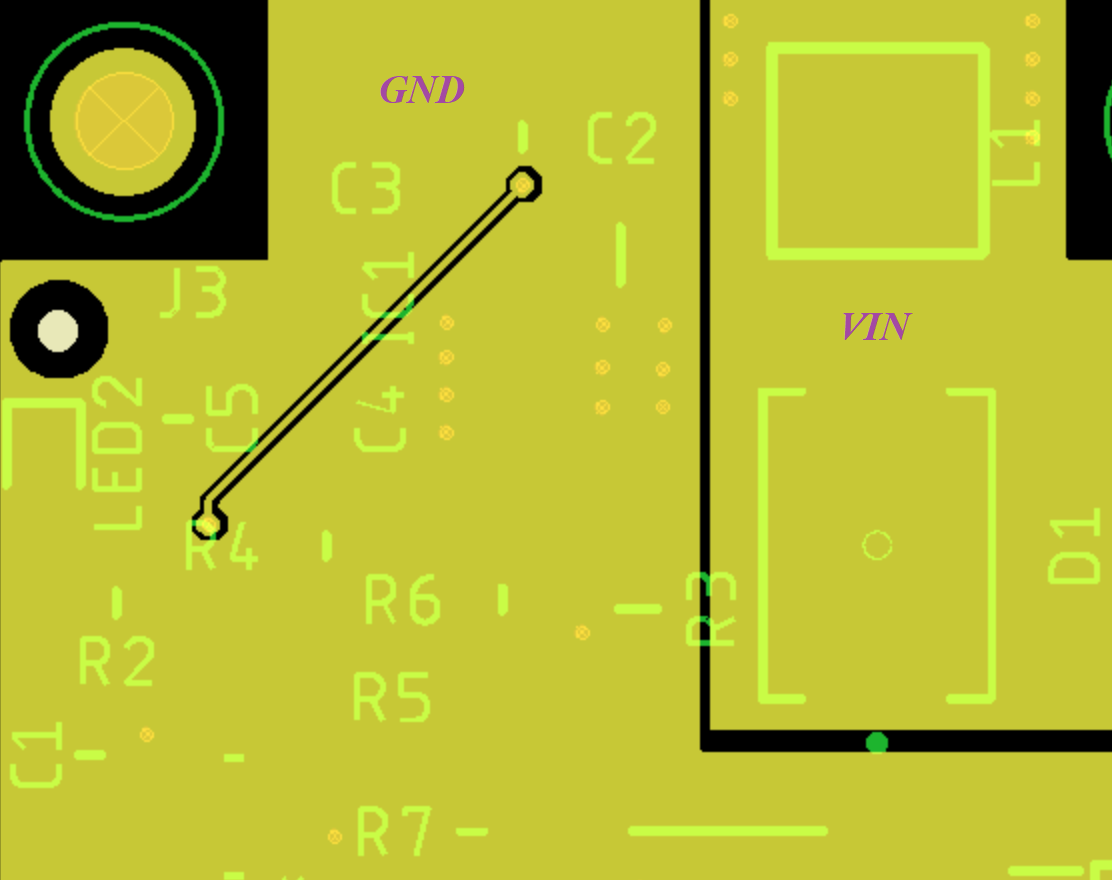

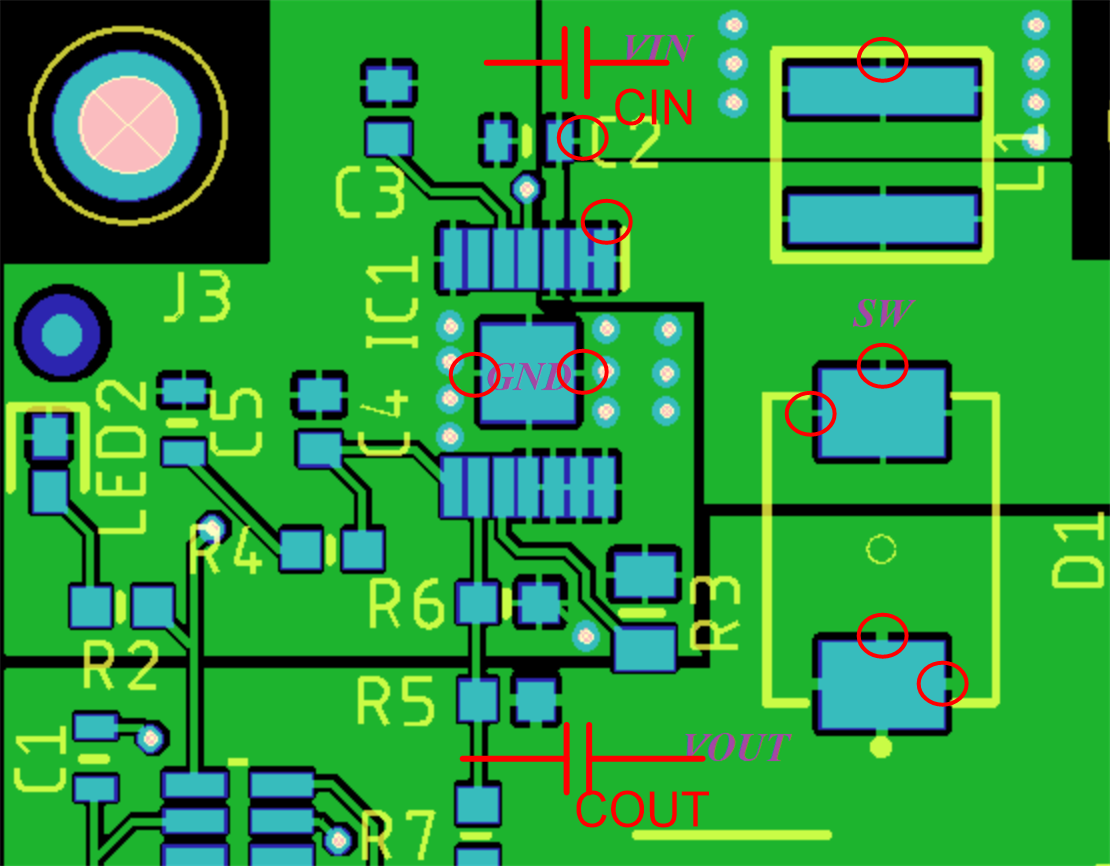

I followed the WEBENCH's schematic and PCB layout for my prototype.

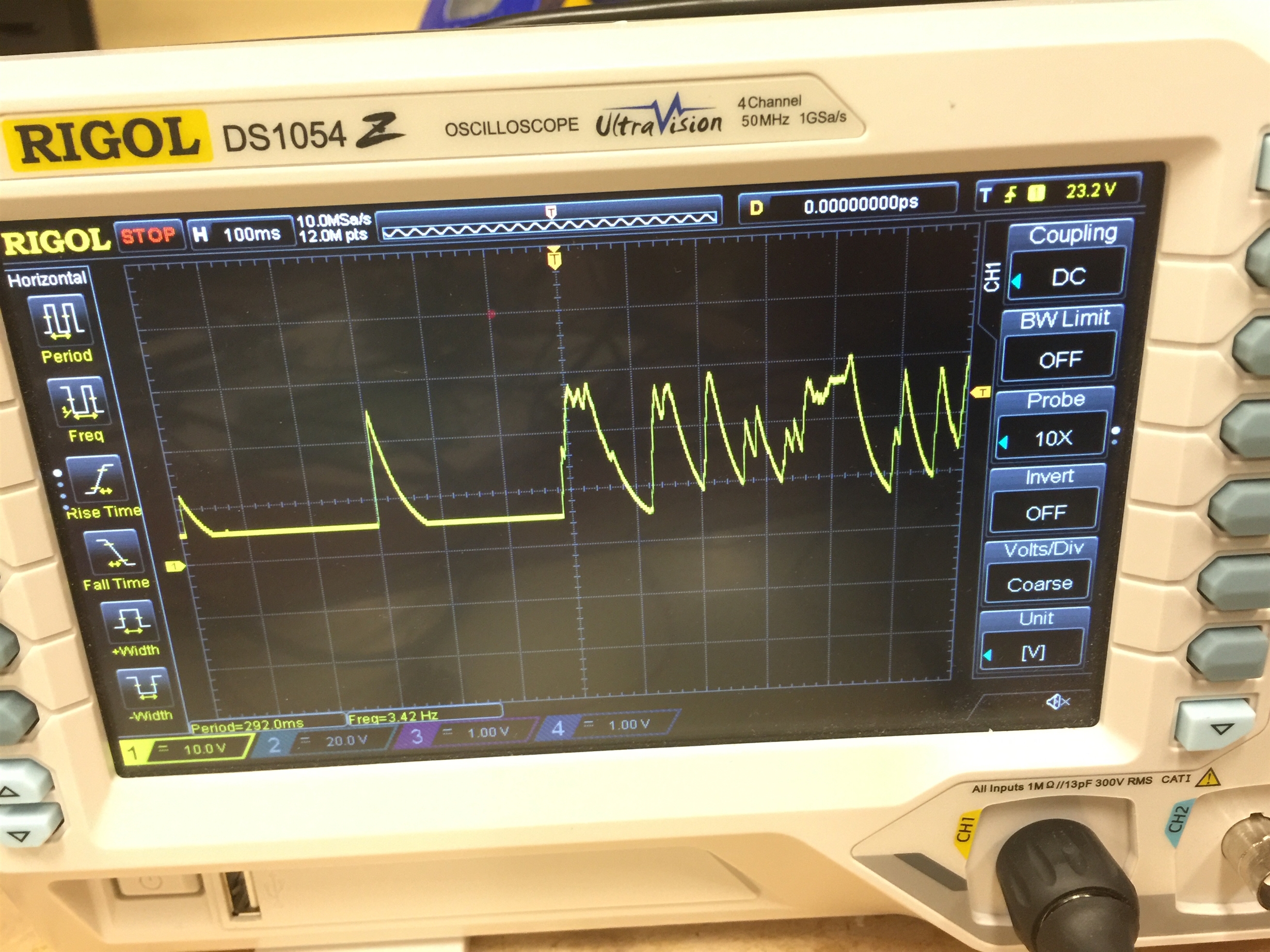

I was expecting to get 30.6V output when I plug the USB 5V input. However, I get an output way lower than 30V.

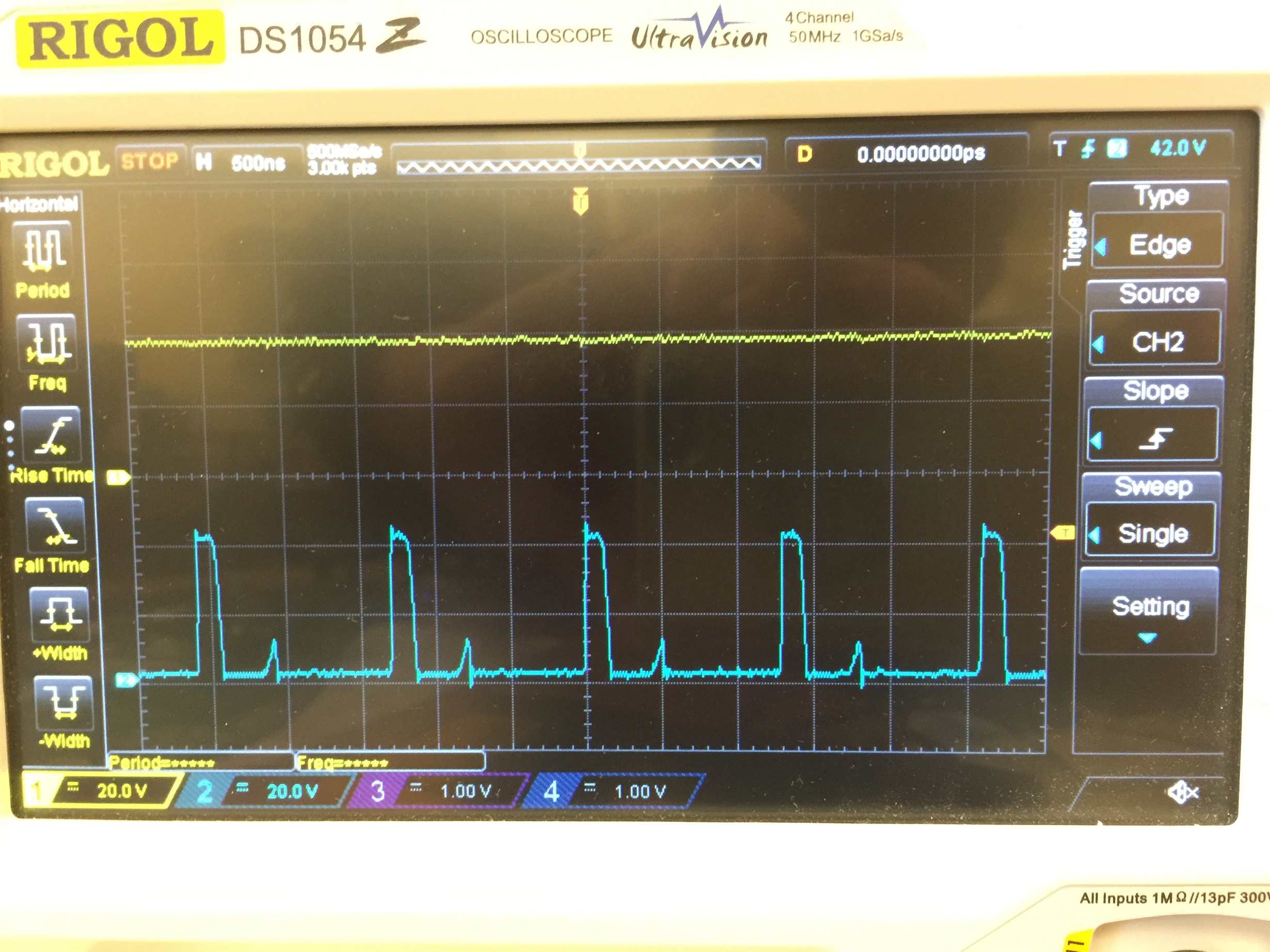

When the "DAC labeled" part is 0V (connected to GND), the output is

0. VIN = USB 5.06V, EN pin = USB 5.06V, VOUT = 9.24V

1. VIN = USB 5.06V, EN pin = 3.288V, VOUT = 4.89V

May I ask

Q0. Why am I getting these output instead of 30.6V? Hope is not a layout issue.

Q1. I wanted to toggle the EN pin using a 3.3V microcontroller.

However, when I connect 3.288V to the EN pin, the output becomes lower than the input voltage.

Does the EN pin has to have the same voltage as the VIN input voltage?

Funny thing is even EN pin is equal to VIN, the output shows an unexpected value.