Hi support,

I recently had an LM73606 destructively fail with a power-to-ground short. I do not see any immediately obvious reasons for this to happen and would like ideas of where to look.

The type of answer which would help me most is a list of causes which may cause the chip to fail in the way described below; including:

- anything that might happen from a hand placement and soldering job, assuming the proper tooling

- input power supply transients

- output power transients

Circuit Description

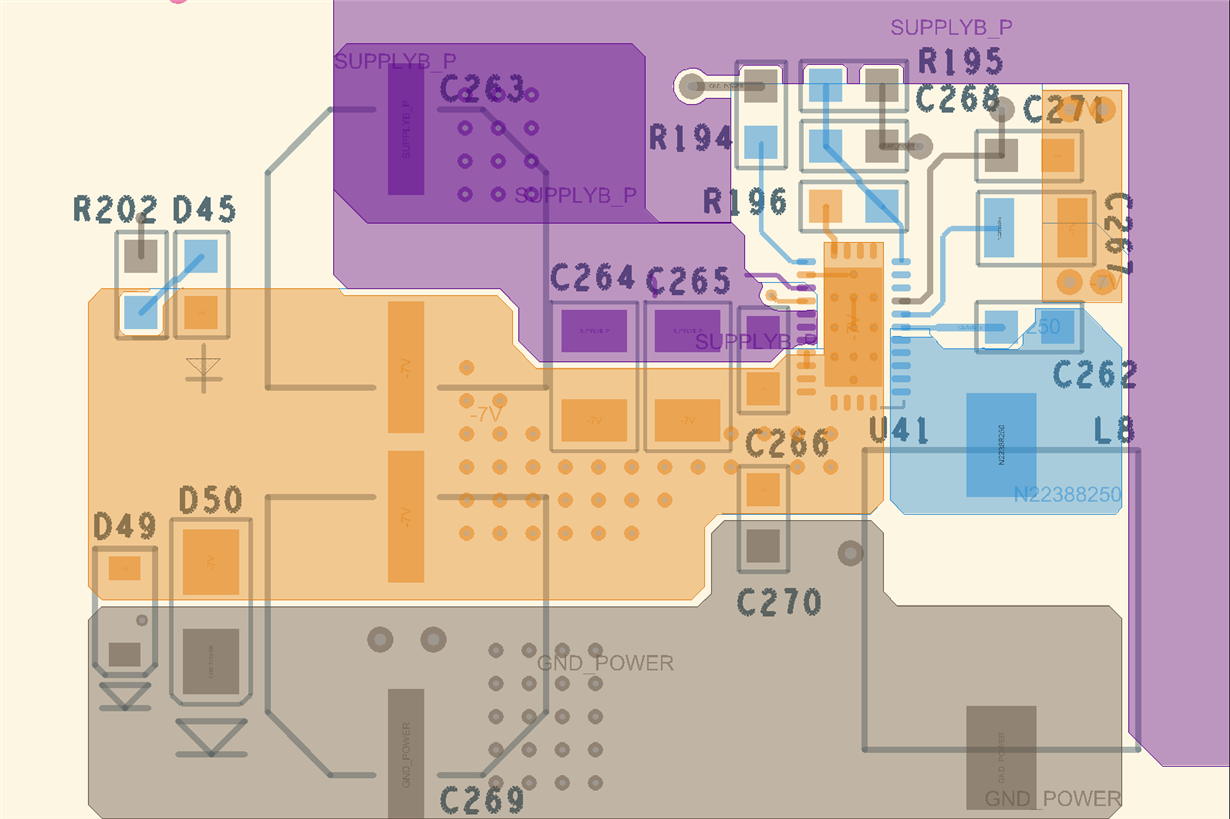

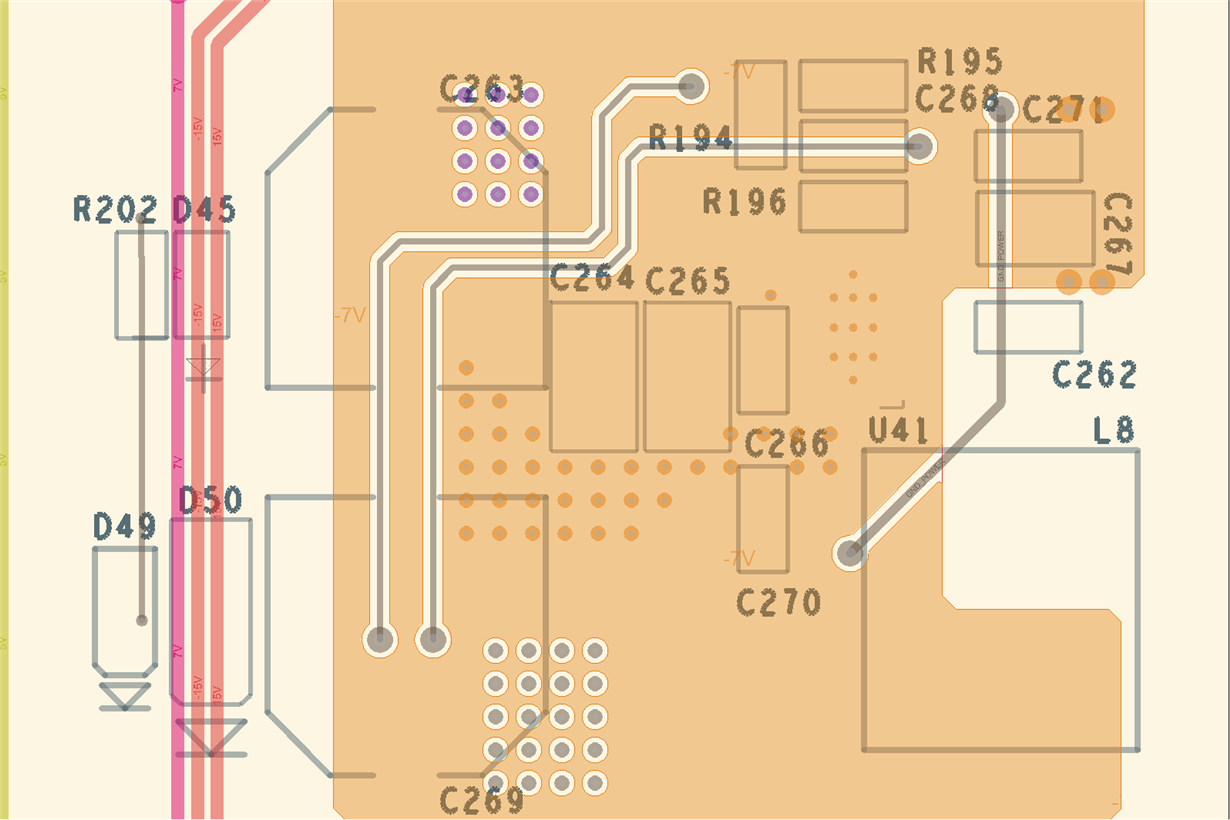

The LM73606 is configured in a ground-referenced buck topology to produce a non-isolated -7V power net. it is used in conjunction with an additional LM73606 to produce a similar +7V power net. Both chips are being powered by the same +24V power supply, which produces a 31V supply for the -7V regulator.

Though I can not attach these portions of the schematic publicly, the converters are being used to power a small number of ADCs and DACs, one linear DC-DC converter each, and a pair of power amplifiers. The power amplifiers are the main current draws in the circuit; the way they are being used should only place a significant draw on one converter at a time. The total current for these operations are well within the LM73606's ratings.

Failure conditions

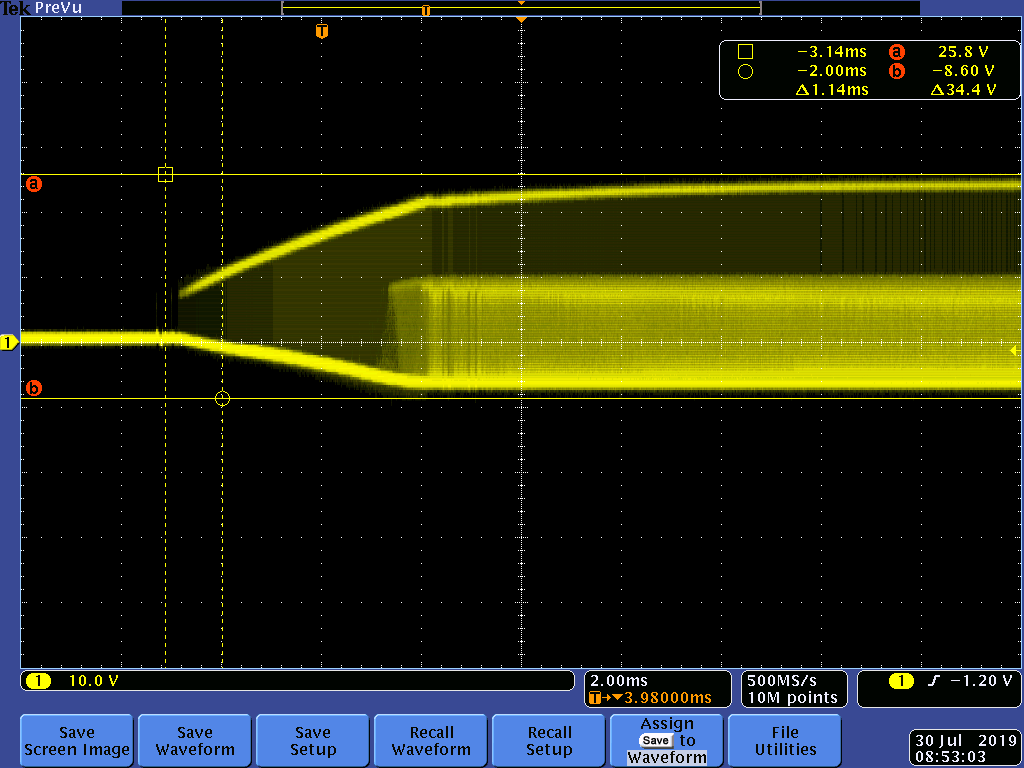

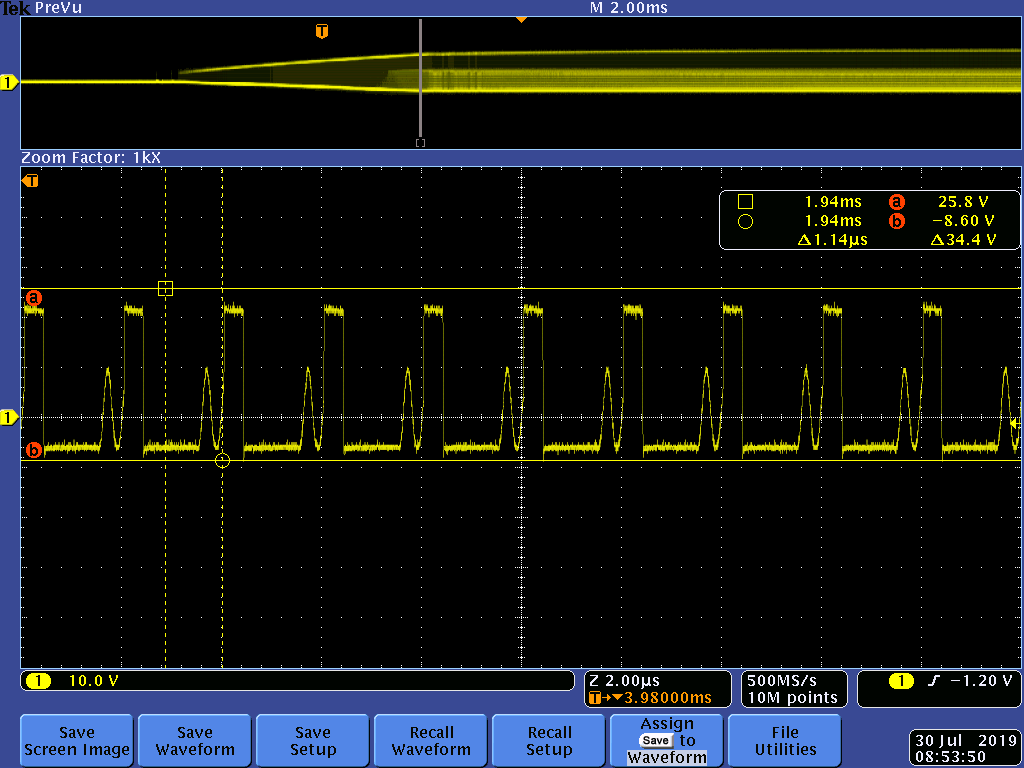

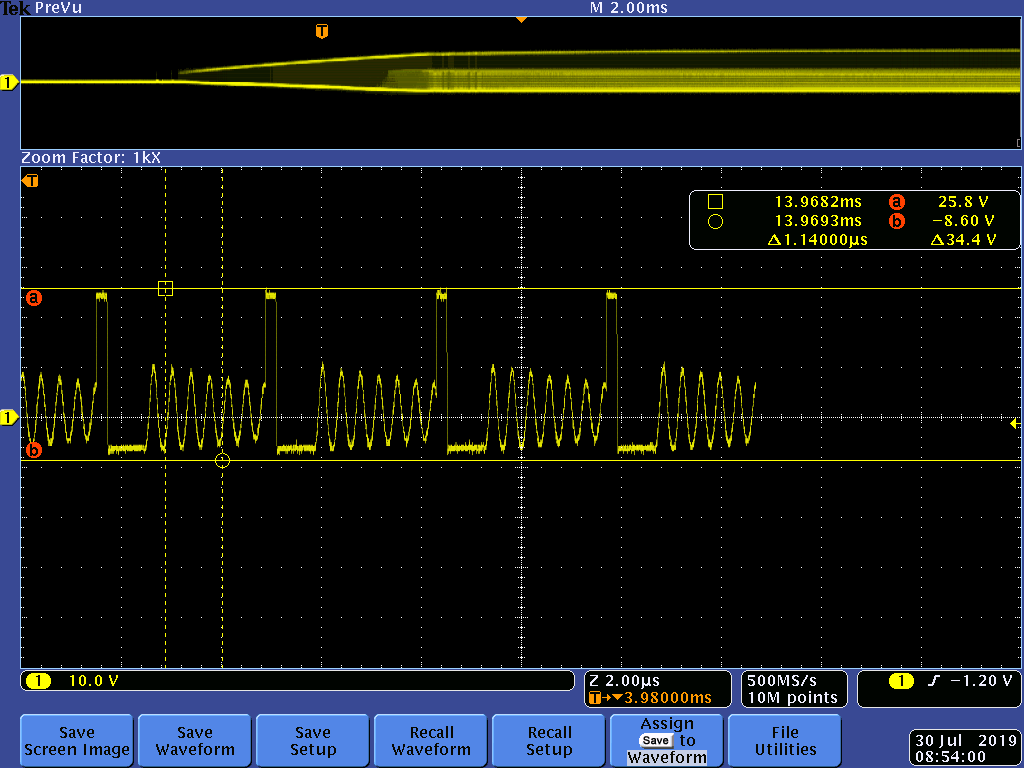

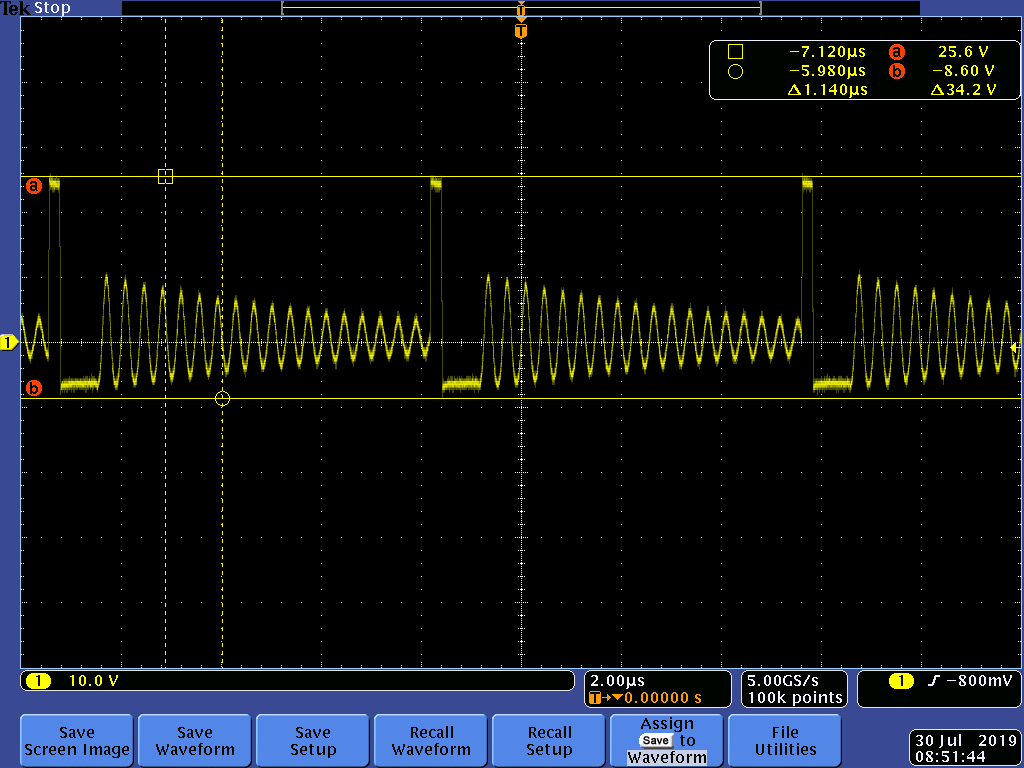

At the time of failure, the failed converter had been powered for roughly 20 minutes and had been operating normally. The output of the power amplifier had been commanded for +20mA, which is to say the failed converter should have been essentially idling.

Now that the converter is failed, there is:

- a 6ohm short from PVin to PGND (nets named SupplyB_P to -7V)

- no short from PVin to the SW node

- no short from SW node to to PGnd

- no additional shorts in the LM73606 to either PVin to PGnd

- no shorts anywhere else in the circuit.

The only potential defect I can see is that there might be poor solder contact on the sync/mode pin.

This one is kind of a head scratcher for me.

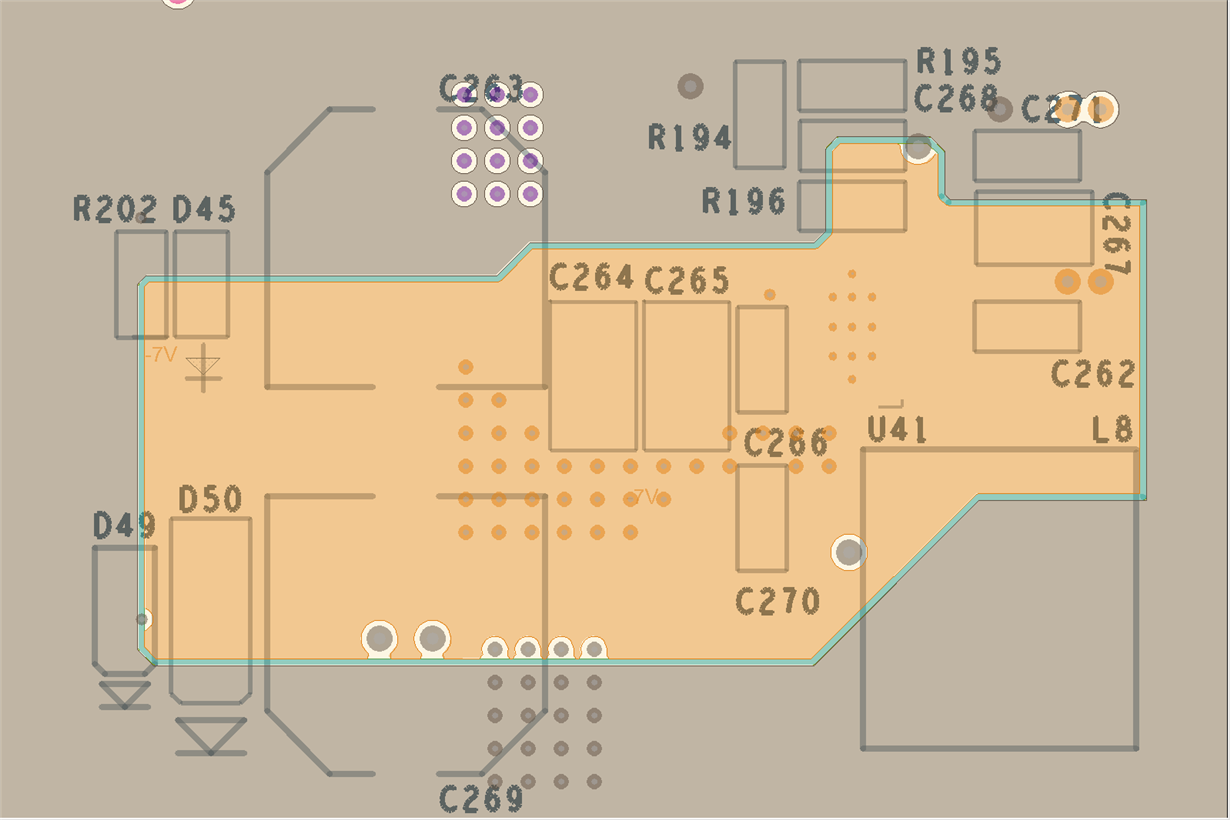

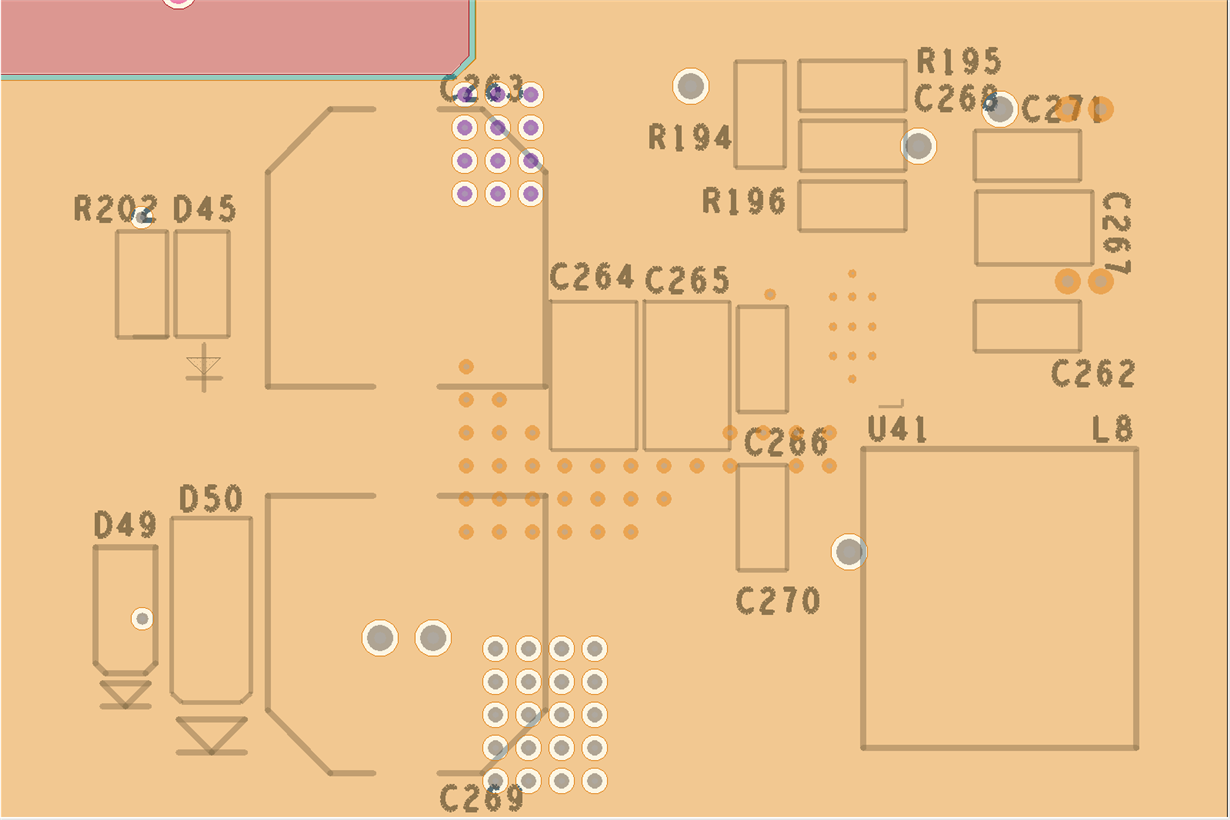

I've attached portions of my schematic detailing the power inlet and the converter itself, images of my layout, and photographs of the failed chip.