Dears,

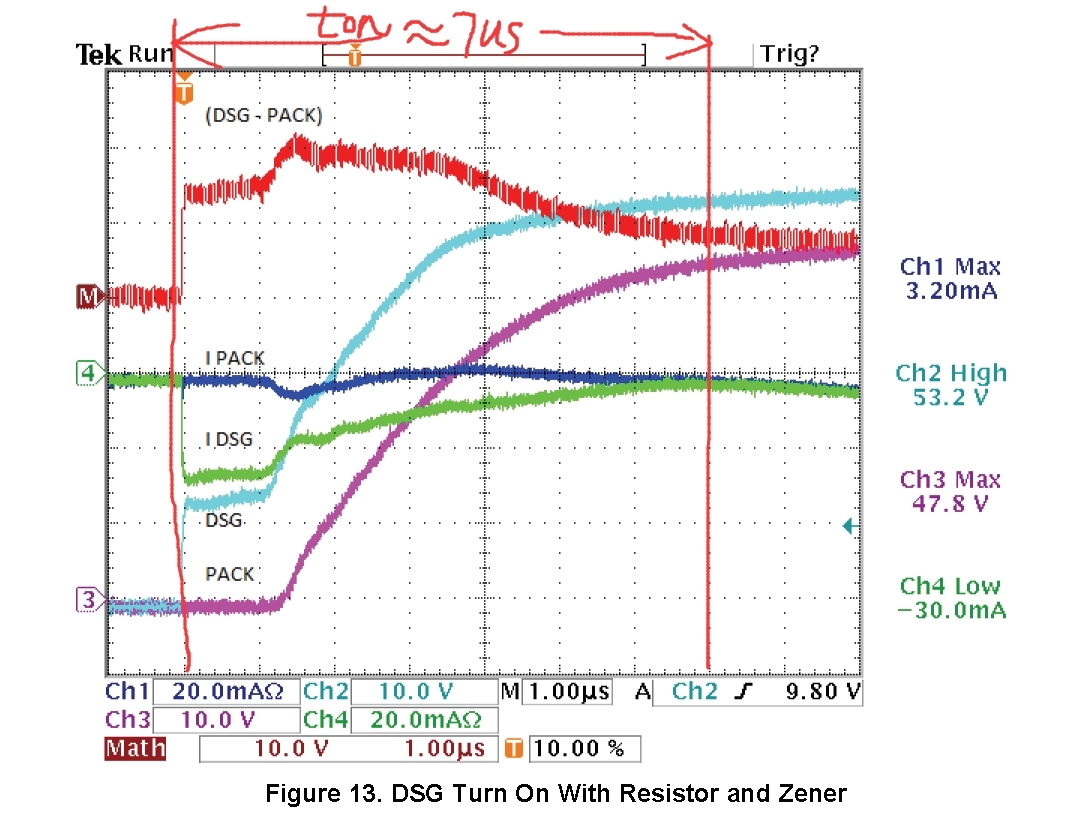

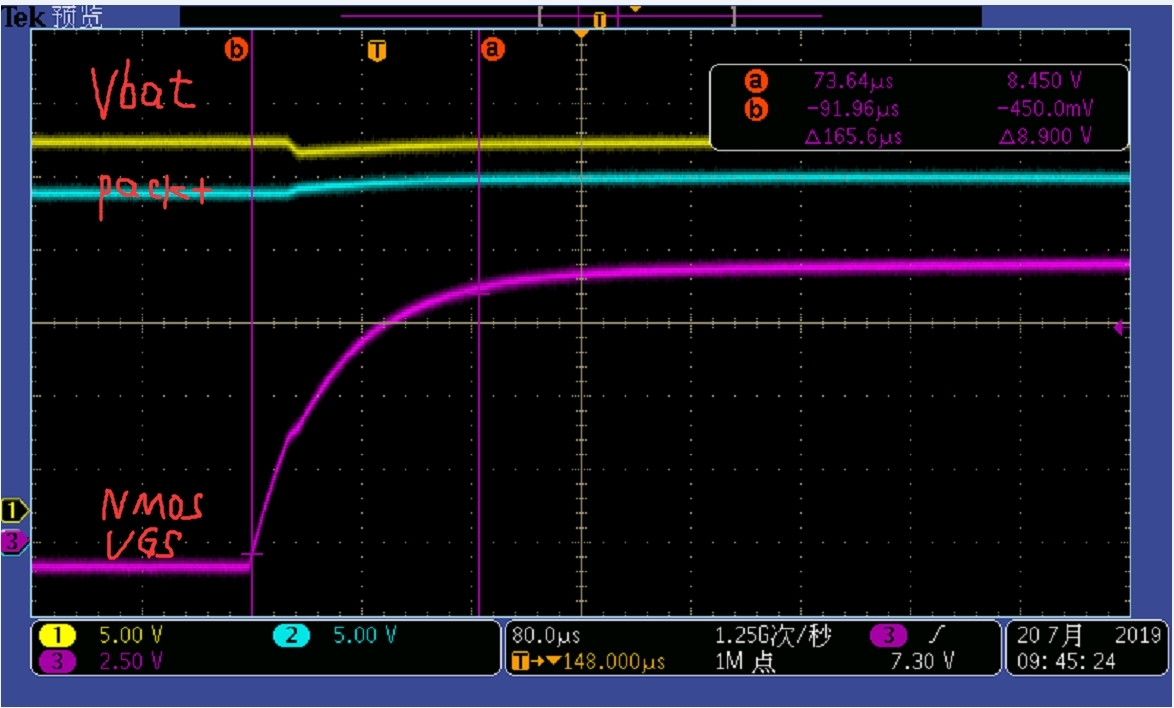

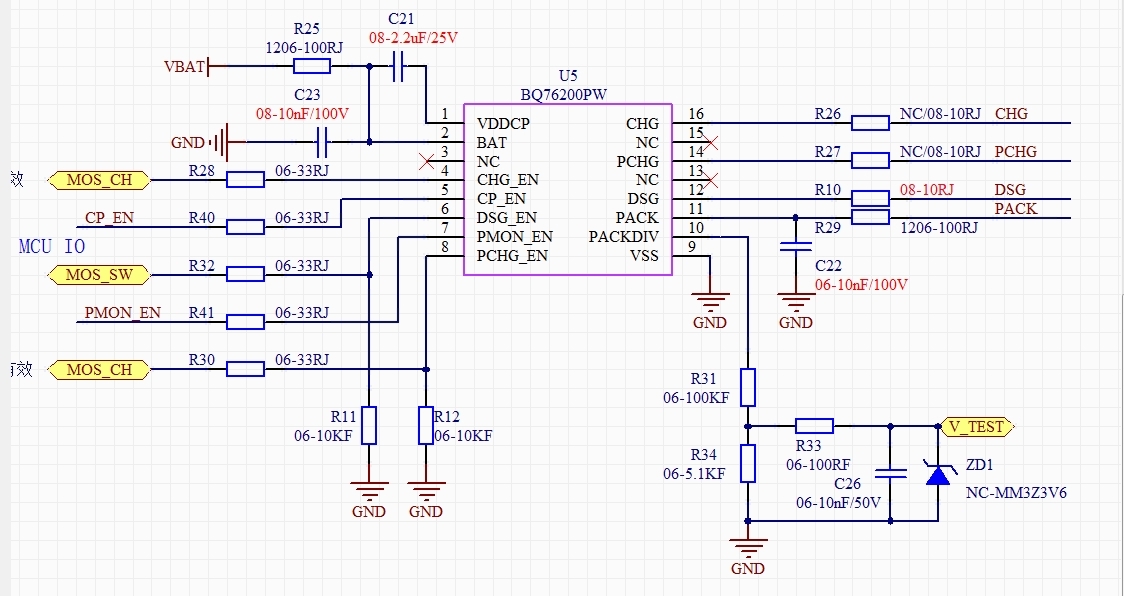

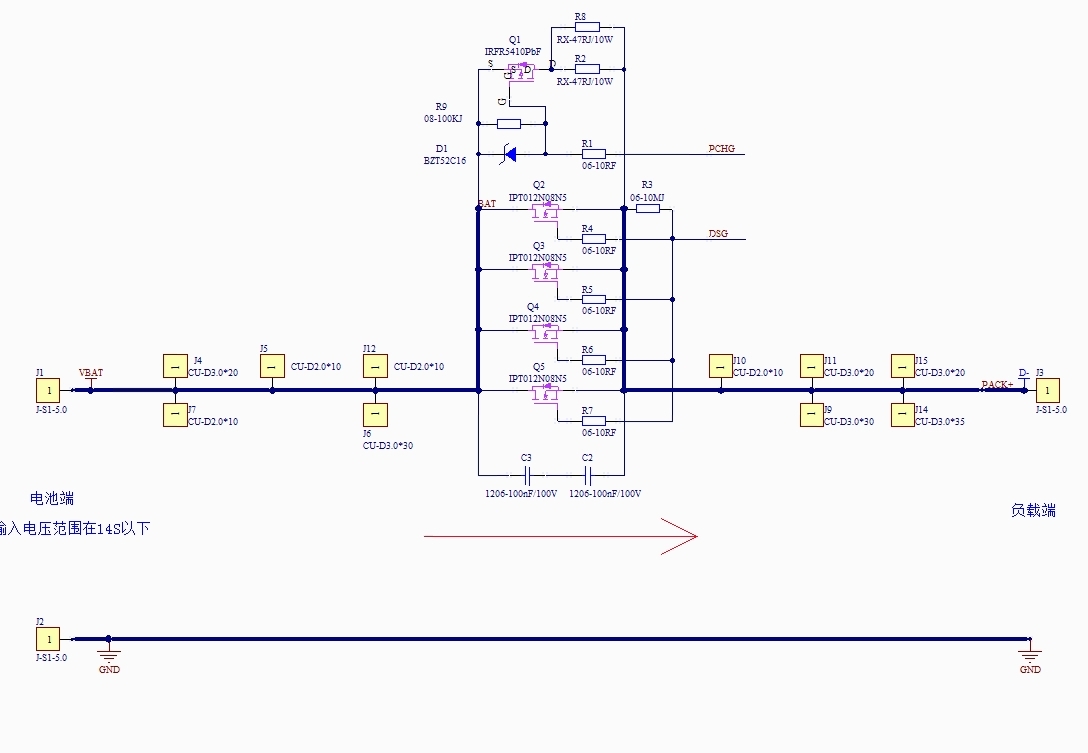

My customer met a issue when they measure the turn ON timing of NMOS(DSG pin of BQ76200). They compared their measured waveform and out spec and found big difference(140us vs 7us). As below left BQ76200 spec, the ton time is about 7us. While as below right waveform, customer measured about 160us. Customer did try to modify external capactior/resistor value, but no any effect... Could you please help check this? Below attached circuit as well.

( NMOS VGS= DSG output)